## Lecture 8 ARM Processor Organization

Spring Term Lecture 8-1

- First ARM processor developed on 3 micron technology in '83-'85

- This course is mainly based on the ARM6/7 architecture developed between '90-'95.

- Digital Equipment Corporation (now Compag) developed the StrongARM processor which has a very high performance.

ISE1/EE2 Computing

Recent developments are: ARM8 and ARM9E (1999), and a ARM processor without clock - the asynchronous AMULET from U. of Manchester (Steve Furber's group)

## Internal Organization of ARM

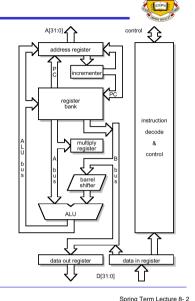

- Two main blocks: datapath and decoder

- Register bank (r0 to r15)

- Two read ports to A-bus/B-bus

- One write port from ALU-bus

- Additional read/write ports for program counter r15

- Barrel shifter shift/rotate 2nd operand by any number of bits

- ALU performs arithmetic/logic functions

pvkc/gac - 13-Nov-01

Address registers/incrementer holds either PC address (with increment) or operand address

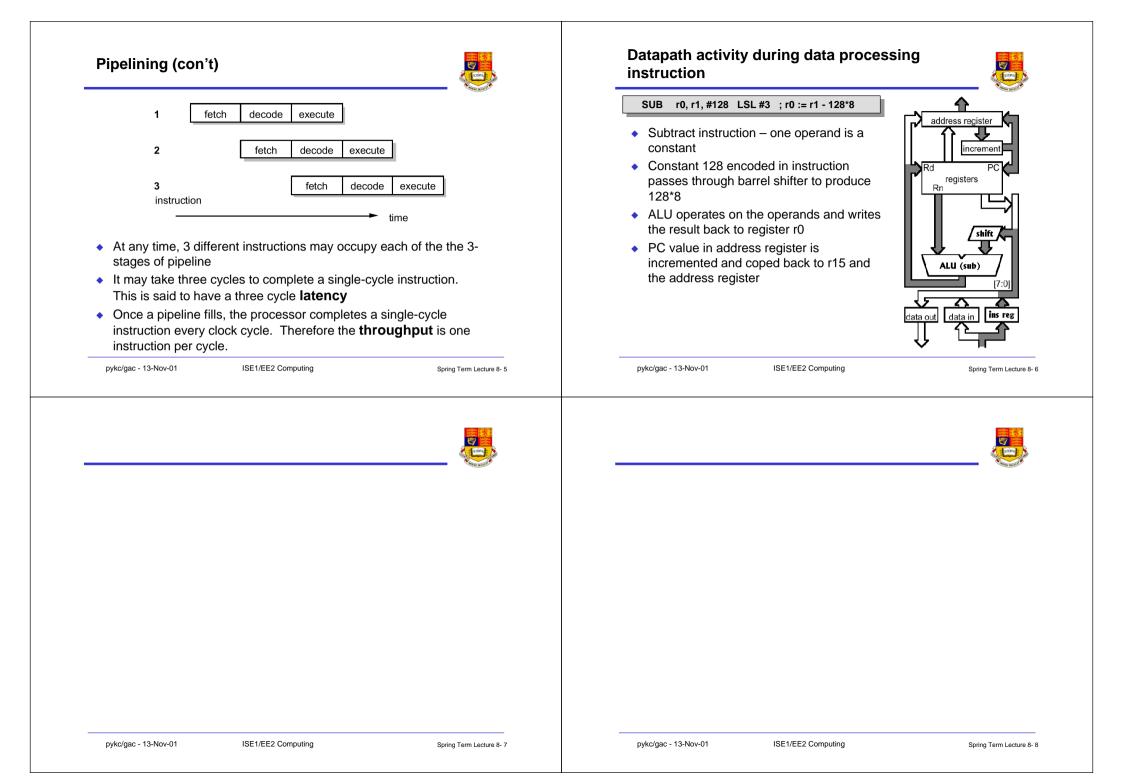

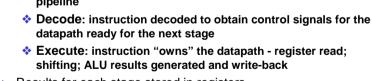

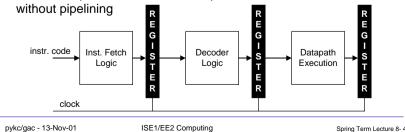

## Pipelining Internal Organization of ARM (con't) A[31:0] 🔨 ARM uses a 3-stage instruction pipeline Data register holds read/write data address register Fetch: fetch instruction code from memory into the instruction from/to memory pipeline Instruction decoder decodes machine code instructions to produce control signals to datapath registe In single-cycle data processing instructio

- instructions, data values are read on the A-bus & B-bus, the results from ALU is written back into register bank

- PC value in address register is incremented and copied back to r15 and the address register - this allows fetching new instructions ahead of time (instruction pre-fetch)

Results for each stage stored in registers

The consequence is that the clock period is much shorter than

ISE1/EE2 Computing

pykc/gac - 13-Nov-01

pvkc/gac - 13-Nov-01

ISE1/EE2 Computing

Spring Term Lecture 8-3