### **Topic 8 - JTAG Boundary Scan**

JTAG (IEEE 1149.1/P1149.4) Tutorial - Introductory

# **JTAG** (IEEE 1149.1/P1149.4) **Tutorial** Introductory

AL 10Sept.-97 1149.1(JTAG)-Tut.I-1

JTAG (IEEE 1149.1/P1149.4) Tutorial - Introductory

# What Is JTAG?

AL 10Sept.-97 1149.1(JTAG)-Tut.I-3

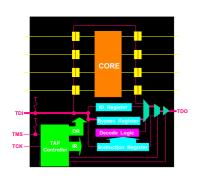

Standard Test Access Port ...

- 4/5-Wire Interface at Chip-Level

- Serial Instruction/Serial Data Port

- Extensible to Include

- user-defined instructions

- user-defined data registers

AL 10Sept.-97 1149.1(JTAG)-Tut.I-5

JTAG (IEEE 1149.1/P1149.4) Tutorial - Introductory

#### **Agenda**

- What Is JTAG? (5 minutes) ■ The Increasing Problem of Test (5 minutes) Conventional Methods of Test (10 minutes) ■ The Boundary-Scan Idea (15 minutes) ■ The Boundary-Scan Architecture (15 minutes) ■ Typical Applications (15 minutes)

- Interconnect Testing

- Logic Cluster Testing

- Memory Testing

- System-Level Test

- (10 minutes) ■ Real JTAG Applications

- For More Information (5 minutes)

- Q & A (10 minutes) AL 10Sept.-97 1149.1(JTAG)-Tut.I-2

1997 TI Test Symposiur

JTAG (IEEE 1149.1/P1149.4) Tutorial - Introductory

## **Standard Approach To Test**

- Developed by Joint Test Action Group (over 200 SC, test, and system vendors) starting in mid '80's

- Sanctioned by IEEE as Std 1149.1 Test Access Port and Boundary-Scan Architecture in 1990

- Solution: Build test facilities/test points into chips

- Focus: Ensure compatibility between all compliant ICs

AL 10Sept.-97 1149.1(JTAG)-Tut.I-4

# JTAG (IEEE 1149.1/P1149.4) Tutorial - Introductory

# ... and Boundary-Scan **Architecture**

- Scan effectively partitions digital logic to facilitate control and observation of its function

- Chip-Internal Scan: Partitions chips at storage cells (latches/ flipflops) to effectively partition sequential logic into clusters of combinational logic

- Boundary-Scan: Partitions boards at chip I/Os for control and observation of board-level nodes

AL 10Sept-97 1149.1(JTAG)-Tut.I-6

# The Increasing **Problem of Test**

AL 10Sept.-97 1149.1(JTAG)-Tut.I-7

# JTAG (IEEE 1149.1/P1149.4) Tutorial - Introductory

# The Incredible Shrinking **Board**

Miniaturization results in loss of test access

Tomorrow?

JTAG (IEEE 1149.1/P1149.4) Tutorial - Introductory

AL 10Sept.-97 1149.1(JTAG)-Tut.I-8

## The Ever-Expanding Chip

■ Increasing integration at chip level complicates controllability

Today

1997 TI Test Symposium

#### **Can't Afford Not To Test**

Cost will increase by a factor of ten as fault finding moves from one level of complexity to the next. The result:

- Reduced Profit Margins

- Delayed Product Introduction

- Dissatisfied Customers

- 1. Device level

- 2. Board level

- 3. System level 4. Field level

- 10 units of cost 100 units of cost

1,000 units of cost

1 unit of cost

1997 TI Test Symposium

AL 10Sept.-97 1149.1(JTAG)-Tut.I-9

JTAG (IEEE 1149.1/P1149.4) Tutorial - Introductory

# Conventional **Methods of Test**

ept.-97 1149.1(JTAG)-Tut.I-10

# **Conventional Methods** of Board Test

Functional Test ('Edge-Connector' Test)

Based on board function, rather than structure

JTAG (IEEE 1149.1/P1149.4) Tutorial - Introductory

- Test generation primarily manual

- Test access limited to primary I/O only

## **Conventional Methods** of Board Test

In-Circuit Test ('Bed-of-Nails' Test)

- Based on board structure, but limited by chip complexity

- Expensive testers and fixtures required

- Test access limited by:

- Fine pitch packages

- Double-sided boards

- Conformal coating

JTAG (IEEE 1149.1/P1149.4) Tutorial - Introductory

## **Conventional Methods** of Board Test

In-Circuit Test ('Bed-of-Nails' Test)

- Chip function can be ignored for shorts testing

- Chip function must be considered for continuity

- Test generation, though automated, requires ICT models

AL 10Sept.-97 1149.1(JTAG)-Tut.I-14

AL 10Sept.-97 1149.1(JTAG)-Tut.I-13

JTAG (IEEE 1149.1/P1149.4) Tutorial - Introductory

JTAG (IEEE 1149.1/P1149.4) Tutorial - Introductory

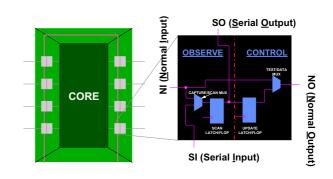

## The **Boundary** Scan Idea

- 'In-Circuit' test points moved onto the silicon, creating 'Virtual Nails'

- Boundary scan cells bound each net, providing for continuity testing

- Observe/Control cells provide for test and normal function

AL 10Sept.-97 1149.1(JTAG)-Tut.I-15

AL 10Sept.-97 1149.1(JTAG)-Tut.I-17

Sept.-97 1149.1(JTAG)-Tut.I-16

JTAG (IEEE 1149.1/P1149.4) Tutorial - Introductory

JTAG (IEEE 1149.1/P1149.4) Tutorial - Introductory

# The Boundary Scan Idea

The

**Boundary-Scan**

ldea

- Scan provides a means to arbitrarily observe test results and source test stimulus

- Scan method requires minimal on chip/board resources (pins/nets)

# **Boundary Scan Method** of Board Test

- Based on board structure; Not limited by chip function/ complexity

- Test access is not limited by board physical factors

AL 10Sept.-97 1149.1(JTAG)-Tut.I-18

# **Boundary Scan Method** of Board Test

Chip function need not be considered for board test (shorted/open nets)

Test generation is highly automated; Simple 'In-Circuit Library' models (BSDL) are vendorsupplied or EDA-generated

AL 10Sept.-97 1149.1(JTAG)-Tut.I-19

AL 10Sept.-97 1149.1(JTAG)-Tut.I-21

AL 10Sept.-97 1149.1(JTAG)-Tut.I-23

JTAG (IEEE 1149.1/P1149.4) Tutorial - Introductory

## The Boundary Scan Cell

AL 10Sept.-97 1149.1(JTAG)-Tut.I-20

JTAG (IEEE 1149.1/P1149.4) Tutorial - Introductory

JTAG (IEEE 1149.1/P1149.4) Tutorial - Introductory

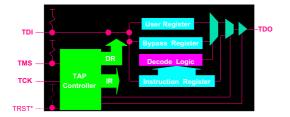

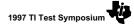

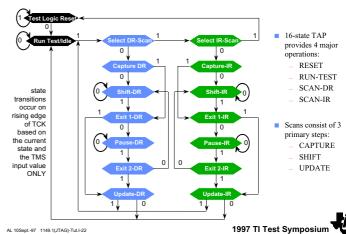

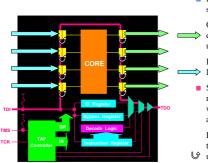

#### **The Control Architecture**

- Boundary scan and other test data registers operate under control of instruction register

- Data is scanned from TDI to TDO through selected test data register or instruction register under control of Test Access Port (TAP) controller

- TAP operates synchronously to TCK using TMS for state selection

# The Test Access Port Controller

1997 TI Test Symposium

JTAG (IEEE 1149.1/P1149.4) Tutorial - Introductory

#### The Extest Instruction (REQUIRED)

Provides for test external to chip, such as interconnect test

Output pins operate in test mode, driven from contents of BSC update latch

Input data captured in BSC scan latches prior to shift operation

Shift operation allows test response to be observed at TDO while next test stimulus inserted

Following shift operation, new test stimulus transferred to BSC U update latches

1997 TI Test Symposium

AL 10Sept.-97 1149.1(JTAG)-Tut.I-24

# The Sample/Preload Instruction

(REQUIRED)

JTAG (IEEE 1149.1/P1149.4) Tutorial - Introductory

in normal mode Input pin data and core logic

Shift operation allows test response to be observed while next test stimulus inserted at TDI

ு Following shift operation, new stimulus transferred to BSC update latches

1997 TI Test Symposium

# The Bypass Instruction (REQUIRED)

- Provides for abbreviated scan path through chip

- Output and input pins operate in normal mode

- The one-bit bypass register is selected for scans

- Mandatory that an all-ones value updated into the IR decodes to Bypass, as well as any opcodes which are otherwise undefined

1997 TI Test Symposium

# Typical JTAG Applications

AL 10Sept.-97 1149.1(JTAG)-Tut.I-26

JTAG (IEEE 1149.1/P1149.4) Tutorial - Introductory

AL 10Sept.-97 1149.1(JTAG)-Tut.I-25

JTAG (IEEE 1149.1/P1149.4) Tutorial - Introductory

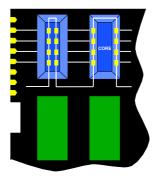

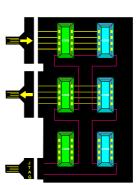

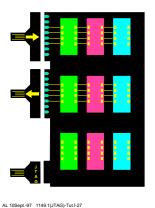

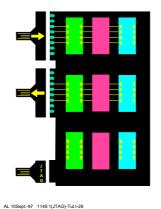

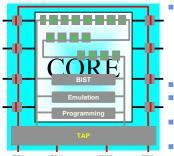

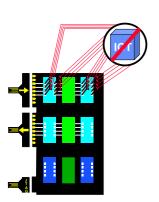

#### **Interconnect Test**

#### Full B/S Board

- All nets bound by BSC's and/or primary I/O requiring no physical access

- Parallel access reduced to card edge only

- Test generation and application fast and easy

FEET

#### Interconnect Test

#### Partial B/S Board

- Not all nets are bound by boundary scan and/or primary I/O, perhaps requiring some ICT access

- Expense and complexity reduced for test generation and test application for chips/nets with B/S access

- Cluster testing may be used to access non-scan nets

JTAG (IEEE 1149.1/P1149.4) Tutorial - Introductory

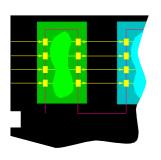

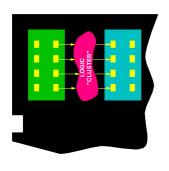

# **Logic Cluster Test**

- Random-logic cluster is bound by boundaryscannable chips

- Deterministic test stimulus (ATPG-generated) can be driven to cluster from B/S outputs

- Test response can be captured at B/S inputs

- BIST methods (PRPG/PSA) can be used for increased test throughput and near "At-speed" performance

1997 TI Test Symposium

# JTAG (IEEE 1149.1/P1149.4) Tutorial - Introductory

# **Logic Cluster Test**

AL 10Sept.-97 1149.1(JTAG)-Tut.I-30

1997 TI Test Symposium

AL 10Sept.-97 1149.1(JTAG)-Tut.I-29

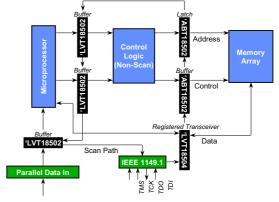

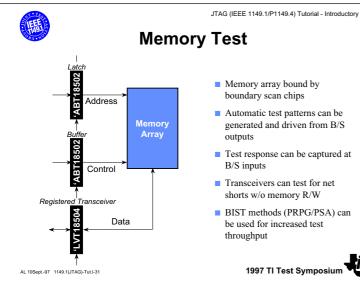

JTAG (IEEE 1149.1/P1149.4) Tutorial - Introductory 鼯 **Memory Test** 375.00 Minute 2,000,000 2,000,000 Time To Apply 5.625000 Seconds Scans 512 IFFF 1149 1 512 512 SAMPLE) IEEE 1149. < 0.01 Minute Time To Apply 0.000041 Seconds 1997 TI Test Symposium

JTAG (IEEE 1149.1/P1149.4) Tutorial - Introductory

- TAP-addressable interface unit extends JTAG access beyond board-level

- System-level test

- System design verification

- Sys integration (Mfg test)

- Sys self-test (Field Svc)

- Supports in place board test and board-to-board test

- Allows reuse of device/ board test data

◆ ASP-Addressable Scan Port Device

AL 10Sept-97 1149.1(JTAG)-Tut.I-33

JTAG (IEEE 1149.1/P1149.4) Tutorial - Introductory

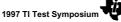

# Real Applications of the TAP

- Scan access to chips, boards, systems for:

- Design verification/debug

- Manufacturing test

- Hardware/software integration

- Field test/diagnostics

- Access built-in self-test (BIST)

- Access on-chip/in-circuit emulation (ONCE/ICE)

- Access in-system programming (ISP) of PLDs/EEPROMs

- Let your imagination run wild!!!

1997 TI Test Symposium

JTAG (IEEE 1149.1/P1149.4) Tutorial - Introductory

# **Real JTAG Applications**

Sept.-97 1149.1(JTAG)-Tut.I-34

# **Design Verification/Debug**

- Provides control and observation of system under test without need for physical access

- Ease of set-up for test

- Can be used in standard system configuration (no need for card extenders, etc.)

- Can be used in environmental chambers

- Can access on-chip emulation for software/debug

- Can access ISP for code download/offload/ changes

AL 10Sept.-97 1149.1(JTAG)-Tut.I-36

1997 TI Test Symposium

# **Manufacturing Test**

- Provides test and diagnostic capabilities of in-circuit test without need/expense of physical access

- Improved fault coverage/diagnostic without large capital expense

- Highly automated test generation reduces test development time

AL 10Sept.-97 1149.1(JTAG)-Tut.I-37

#### JTAG (IEEE 1149.1/P1149.4) Tutorial - Introductory

# **System Configuration Maintenance**

- Provides low-level test access within configured systems for:

- In-house system integration

- Fielded-system test and diagnostics

- Built-in self-test

- In-field upgradability via ISP, etc.

- Remote field test. diagnostic and upgrade

AL 10Sept.-97 1149.1(JTAG)-Tut.I-38

JTAG (IEEE 1149.1/P1149.4) Tutorial - Introductory

#### **TI's JTAG Educational Products** Call (214)-638-0333 to ORDER

- Scan Educator

- PC-based tutorial with interactive boundary-scan simulation.

- FREE download at http://www.ti.com/sc/data/jtag/scanedu.exe

- Two-part video presenting an overview and instructions for boundary scan.

- Item No. SATV001 (NTSC VHS) and SATV002 (PAL VHS), \$149 each.

- In process of converting to MPEG on CD-ROM

JTAG (IEEE 1149.1/P1149.4) Tutorial - Introductory

AL 10Sept.-97 1149.1(JTAG)-Tut.I-40

# **Tutorials/Handbooks**

- The Test Access Port and Boundary-Scan Architecture, Colin M. Maunder, Rodham E. Tulloss, ed., IEEE CS Press, ISBN 0-8186-9070-4.

- Edited by two principal chairs of the IEEE 1149.1 working group, this Computer Society tutorial compiles several of the seminal papers on boundaryscan along with several invited papers on various topics including applications, implementation, and others. It will primarily be of interest to the design and/or test engineer.

- <u>The Boundary-Scan Handbook</u>, Kenneth P. Parker, Kluwer Academic Publishers, ISBN 0-7923-9270-1.

- Authored by the principal force behind the Boundary-Scan Description Language (BSDL) and an IEEE 1149.1 working group principal as well as a long time manufacturing and design-for-test expert, this is truly considered THE indispensable handbook on boundary scan for the design and/or test engineer.

- Boundary-Scan Test A Practical Approach, Harry Bleeker, Peter van den Eijnden, Frans de Jong, Kluwer Academic Publishers, ISBN 0-792-9296-5.

- Authored by several JTAG and IEEE 1149.1 working group principals, this book is a ready reference to boundary-scan technology, its benefits, and considerations for design and test managers and engineers.

1997 TI Test Symposium

JTAG (IEEE 1149.1/P1149.4) Tutorial - Introductory

#### **IEEE Standards** Call (800) 678-IEEE to ORDER

■ IEEE Std 1149.1-1990 (Includes IEEE Std 1149.1a-1993), IEEE Standard Test Access Port and Boundary-Scan Architecture, ISBN 1-55937-350-4, IEEE order number SH16626.

- The official document which specifies the international standard for a test access port and boundary-scan architecture. Informally known as the JTAG standard, it was officially ratified by the IEEE in February 1990. Since, it has been supplemented twice. The first supplement, ratified in June 1993, is included in the referenced document. The second supplement is currently  $\boldsymbol{a}$ separate document, as referenced below.

- IEEE Std 1149.1b-1994, Supplement to IEEE Std 1149.1-1990, ISBN 1-55937-497-7, IEEE order number SH94256

- The official document which specifies the international standard for a boundary-scan description language. This supplement to IEEE Std 1149.1-1990 was ratified in September 1994.

ept.-97 1149.1(JTAG)-Tut.I-42

JTAG (IEEE 1149.1/P1149.4) Tutorial - Introductory

AL 10Sept.-97 1149.1(JTAG)-Tut.I-46

#### Abbreviations/Acronyms

| ASIC | Application-Specific Integrated Circuit | IEEE | Institute of Electrical & Electronics Engineers IR |

|------|-----------------------------------------|------|----------------------------------------------------|

| ASP  | Addressable Scan Port                   |      | Instruction Register                               |

| ATE  | Automatic Test Equipment                | ISP  | In-System Programming                              |

| ATPG | Automatic Test Pattern Generation       | JTAG | Joint Test Action Group                            |

| BIST | Built-In Self-Test                      | MCM  | Multi-Chip Module                                  |

| B/S  | Boundary-Scan                           | Mfg  | Manufacturing                                      |

| BSC  | Boundary-Scan Cell                      | PCB  | Printed Circuit Board                              |

| BSDL | Boundary-Scan Description Language      | PLD  | Programmable Logic Device                          |

| BSR  | Boundary-Scan Register                  | PRPG | Pseudo-Random Pattern Generation                   |

| BST  | Boundary-Scan Test                      | PSA  | Parallel Signature Analysis                        |

| CAE  | Computer-Aided Engineering              | PWB  | Printed Wiring Board                               |

| DFT  | Design-for-Test                         | SPL  | Scan Path Linker                                   |

| DR   | Data Register                           | SVF  | Serial Vector Format                               |

| DSP  | Digital Signal Processing/Processor     | TAP  | Test Access Port                                   |

| EDA  | Electronic Design Automation            | TBC  | Test Bus Controller                                |

| eTBC | Embedded Test Bus Controller            | TCK  | Test Clock                                         |

| FPGA | Field-Programmable Gate Array           | TDI  | Test Data Input                                    |

| HSDL | Hierarchical Scan Description Language  | TDO  | Test Data Output                                   |

| ICE  | In-Circuit Emulation                    | TMS  | Test Mode Select                                   |

| ICT  | In-Circuit Test                         | TRST | Test Reset                                         |

|      |                                         | UUT  | Unit Under Test                                    |

|      |                                         |      | <b></b> (1)                                        |

1997 TI Test Symposium

AL 10Sept.-97 1149.1(JTAG)-Tut.I-43