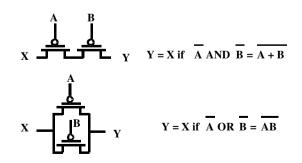

#### PMOS switch closes when switch control input is low

PMOS Transistors pass a "strong" 1 but a "weak" 0

• Complementary pull-up (p-type) and pull-down (n-type)

E4.20 Digital IC Design

Lecture 6 - 4

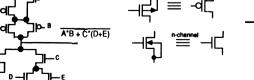

### **Static CMOS**

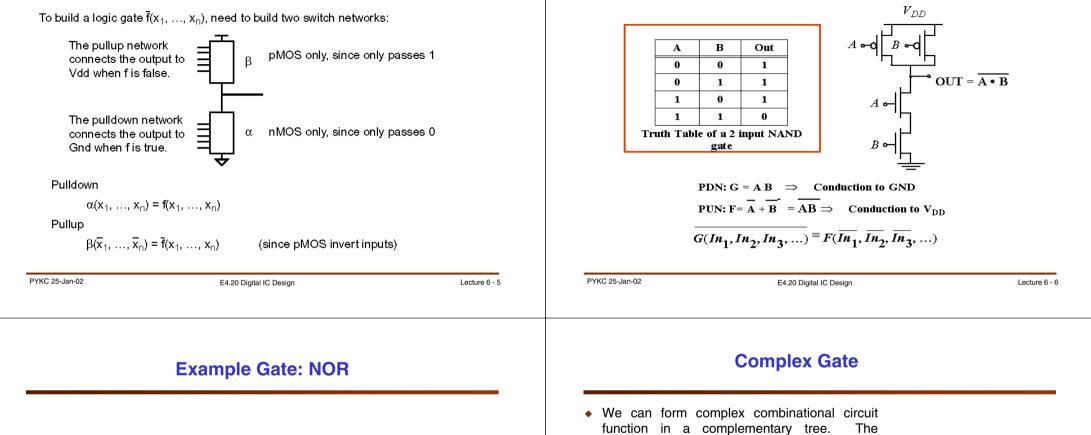

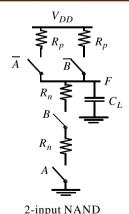

### **Example Gate: NAND**

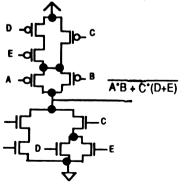

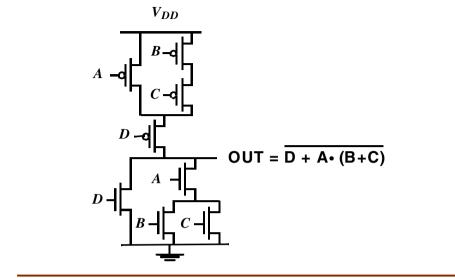

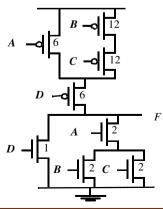

function in a complementary tree. The procedure to construct a complementary tree is as follow:-

- Express the boolean expression in an inverted form

- For the n-transistor tree, working from the innermost bracket to the outer-most term, connect the **OR** term transistors in parallel, and the **AND** term transistors in series

- For the p-transistor tree, working from the innermost bracket to the outer-most term, connect the OR term transistors in series, and the AND term transistors in parallel

в

0

1

0

1

Truth Table of a 2 input NOR gate

A

0

0

1

1

Out

1

0

0

0

$OUT = \overline{A + B}$

#### Example Gate: COMPLEX CMOS GATE

### **Properties of Complementary CMOS Gates**

1) High noise margins

$V_{OH}$  and  $V_{OL}$  are at  $V_{DD}$  and GND, respectively.

2) No static power consumption

There never exists a direct path between  $V_{DD}$  and  $V_{SS}(GND)$  in steady-state mode

*3) Comparable rise and fall times:* (under the appropriate scaling conditions)

### **Transistor Sizing**

- for symmetrical response (dc, ac)

- for performance

- $V_{DD}$

#### **Input Dependent**

Focus on worst-case

• assume  $\mu_n = 3^* \mu_p$  (i.e. n-channel transistors has 3 times the transconductance as that of p-channel.)

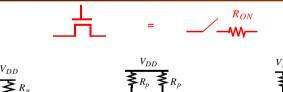

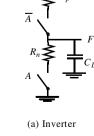

### **Propagation Delay Analysis - The Switch Model**

(c) 2-input NOR

$t_p = 0.69 R_{on} C_L$

#### (assuming that C<sub>L</sub> dominates!)

Lecture 6 - 11

PYKC 25-Jan-02

### What is the Value of *R*<sub>on</sub>?

- Depends strongly on the operating region

- For hand analysis use a fixed value of R which it the average of the two end points of the transition

- Similar to the previous approach of averaging currents

### **EXAMPLE:** For $t_{\text{pHL}}$ for an inverter, the $R_{\text{on}}$ is:

$$R_{on} = \frac{1}{2} (R_{NMOS}(V_{out} = V_{DD}) + R_{NMOS}(V_{out} = V_{DD}/2))$$

$$= \frac{1}{2} \left( \left( \frac{V_{DS}}{I_D} \right)_{V_{out}} = V_{DD} + \left( \frac{V_{DS}}{I_D} \right)_{V_{out}} = V_{DD}/2 \right)$$

### Numerical Examples of Resistances for 1.2µm CMOS

$V_{DD} = 5V$ , W/Leff=1 (W/L<sub>eff</sub>=2 is a minimum sized device 1.8µm/0.9µm)  $L_{eff} = 1.2 \mu m - 2(.15 \mu m) = 0.9 \mu m$

$R_n(W/L_{eff}=2) = (5 \text{ V} / 0.46 \text{ mA} + 2.5 \text{ V} / 0.29 \text{ mA}) / 2 = 9.7 \text{ k}\Omega \text{ (for } t_{pHL})$  $R_n(W/L_{eff}=1) = 9.7 * 2 = 19.4 \text{ k}\Omega \text{ (for } t_{pHL})$

$R_p(W/L_{eff}=6) = (5 \text{ V} / 0.57 \text{ mA} + 2.5 \text{ V} / 0.24 \text{ mA}) / 2 = 9.6 \text{ k}\Omega \text{ (for } t_{pLH})$  $R_p(W/L_{eff}=1) = 9.6 * 6 = 57.6 \text{ k}\Omega \text{ (for } t_{pLH})$

#### For this process, Wp = 3\*Wn for the same resistance

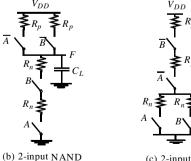

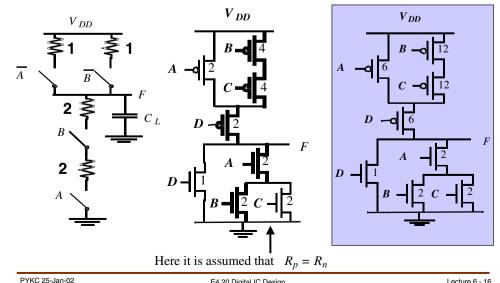

### **Analysis of Propagation Delay**

1. Assume  $R_p = R_p$  = resistance of minimum sized NMOS inverter

- 2. Determine "Worst Case Input" transition (Delay depends on input values)

- 3. Example: t<sub>pl H</sub> for 2input NAND

- Worst case when only ONE PMOS Pulls up the output node

- For 2 PMOS devices in parallel, the resistance is lower

$t_{n/H} = 0.69 R_n C_l$

4. Example: t<sub>pHL</sub> for 2input NAND - Worst case : TWO NMOS in series

$t_{pHL} = 0.69(2R_n)C_1$

### **Design for Worst Case**

PYKC 25-Jan-02

### Fast Complex Gate - Design Techniques

• Transistor Sizing:

As long as Fan-out Capacitance dominates

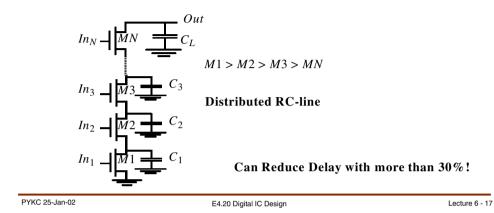

• Progressive Sizing:

### Fast Complex Gate - Design Techniques (3)

• Improved Logic Design

### Fast Complex Gate - Design Techniques (2)

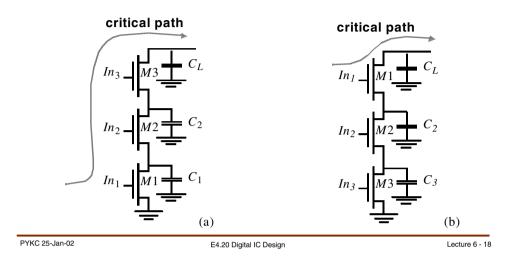

• Transistor Ordering

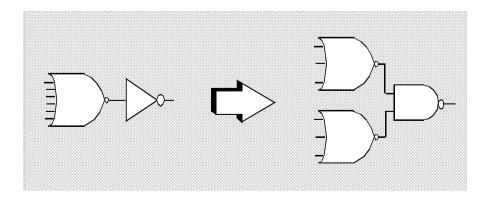

#### Fast Complex Gate - Design Techniques (4)

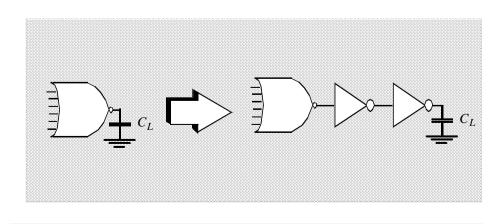

• Buffering: Isolate Fan-in from Fan-out

Lecture 6 - 19

PYKC 25-Jan-02

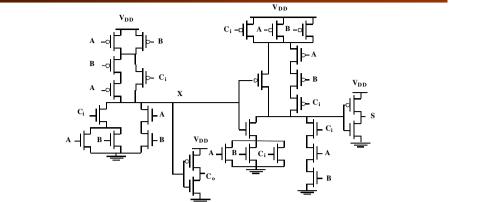

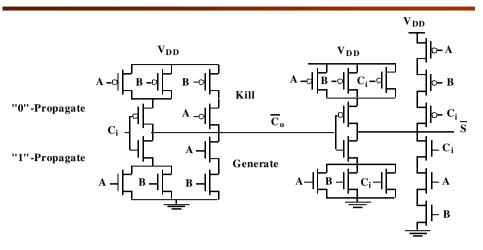

$C_o = AB + C_i(A+B)$

#### A Revised Adder Circuit

### 24 transistors

#### 28 transistors PYKC 25-Jan-02 E4.20 Digital IC Design Lecture 6 - 21 PYKC 25-Jan-02 Lecture 6 - 22 E4.20 Digital IC Design

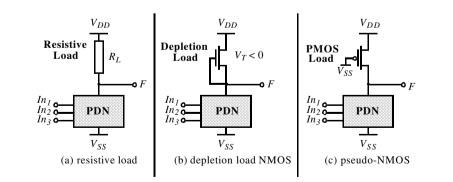

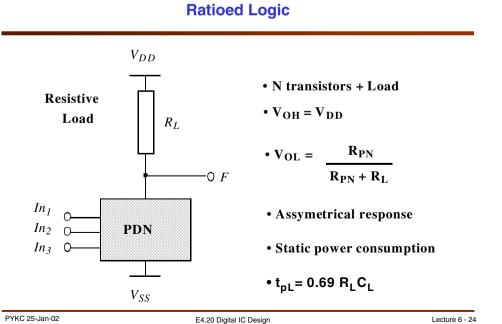

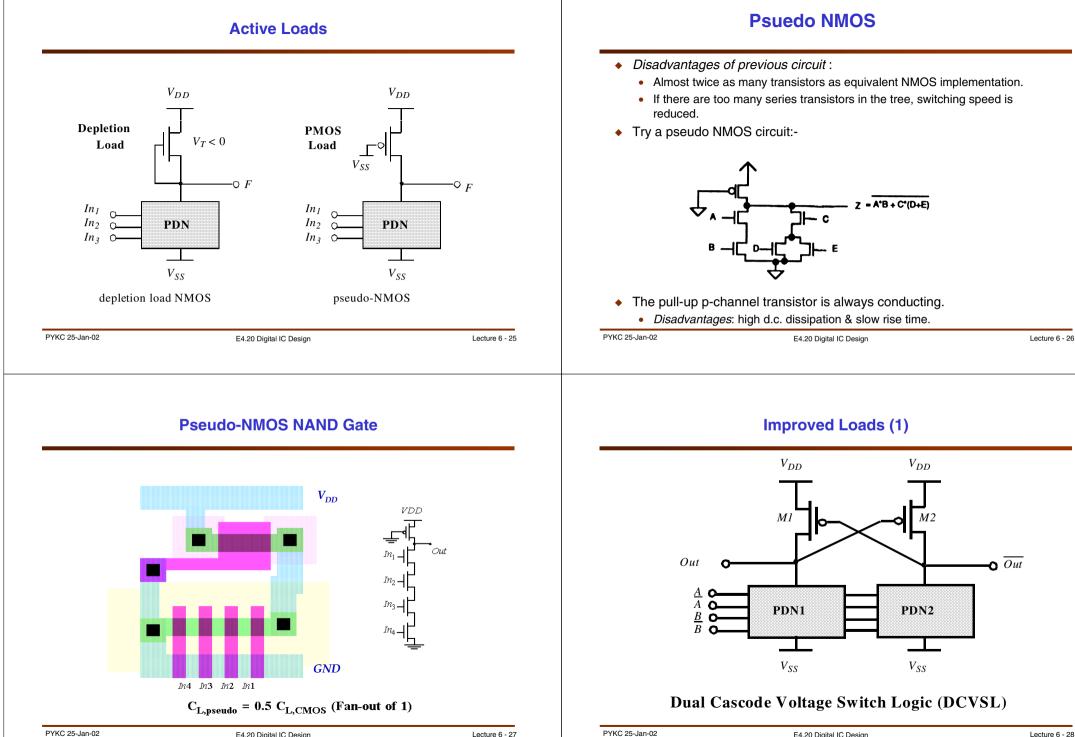

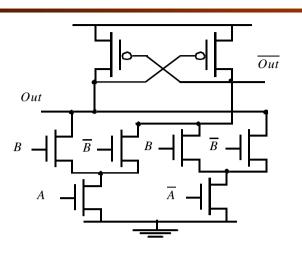

### **Ratioed Logic**

Goal: to reduce the number of devices over complementary CMOS

#### Example

### XOR-NXOR gate

PYKC 25-Jan-02 E4.20 Digital IC Design

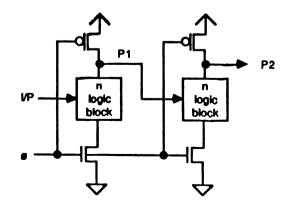

### **Problem with Cascading Dynamic Logic**

- Problem with cascading such as a circuit:-

- Inputs can only be changed when Ø is low and must be stable when Ø is high.

- When Ø is low, both P1 and P2 are precharged to a high voltage. However when Ø is high, delay through on the output P1 may erroneously discharge P2.

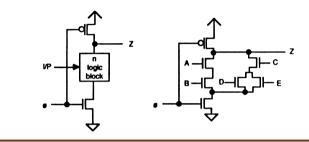

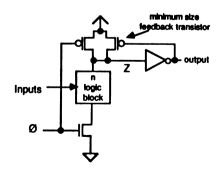

### **Dynamic Logic**

- There is another class of logic gates which relies on the use of a clock signal. This class of circuit is known as *dynamic circuits*. The clock signal is used to divide the gate operation into two halves. In the first half, the output node is *pre-charged* to a high or low logic state. In the second half of a clock cycle, the circuit *evaluates* the correct output state.

- When Ø is low, Z is charged to high. When Ø is high, n logic block evaluates input, and conditionally discharges Z. This circuit adds series resistance to the pull-down n-channel transistor, therefore the fall time is increased slightly.

- This circuit is *dynamic* because during evaluation, the output high level at Z is maintained by the stray capacitance at the output node. If Ø stays high (i.e. evaluation period) for a long time, Z may eventually discharge to a low logic level.

PYKC 25-Jan-02

E4.20 Digital IC Design

Lecture 6 - 30

## **CMOS Domino Logic**

- Solution to the above problem:-

- Add an inverter to ensure that the output is low during precharge, and prevent the next stage from evaluating, until the current stage has finished evaluation.

- This ensures that each stage (at the output of the inverter) will make at most a single transition from 0 -> 1.

- When many stages are cascaded, evaluation proceeds from one stage to the next similar to dominos falling one after another.

- Disadvantages of domino logic:-

- Only non-inverting logic is possible, i.e. outpu also high active

- Each gate needs an inverter; hence more transistors

- Suffer from charge sharing effect (considerec later)

Lecture 6 - 31

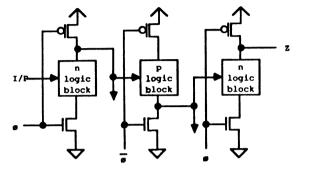

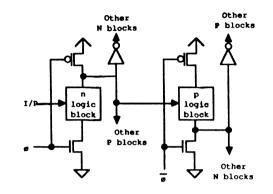

### Alternating dynamic logic (1)

- Another possible scheme is to use alternate n and p logic blocks as shown below.

- In this scheme, each alternate stage is pre-charged high and low. Each stage uses alternate n and p transistors to implement the gate function. Stage 1 makes at most one high to low transition, while stage 2 makes at most one low to high transition for each evaluation. Since the p logic block will only change state if input is a low, this circuit behaves like the domino logic.

# PYKC 25-Jan-02 E4.20 Digital IC Design Lecture 6 - 33 PYKC 25-Jan-02

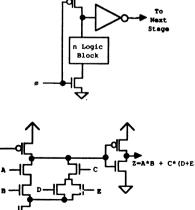

### Making a Dynamic Gate static

- Finally, by adding a feedback pullup, we can make the circuit static.

- This circuit turns the originally *dynamic* gate into a *static* gate because the feedback transistor can maintain a logic high level at the node Z for an indefinite length of time. Without this feedback transistor, the charge stored at the node Z will eventually leak away.

## Alternating dynamic logic (2)

A slight variation of this circuit is show below, where an inverter is added per stage to increase flexibility. Here each stage can drive either n or p blocks and both low active and high active logic can be implemented.

E4.20 Digital IC Design

Lecture 6 - 34

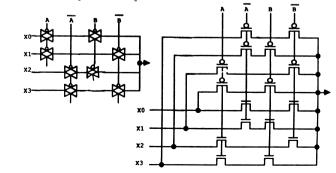

### **Pass Transistor Logic**

- An alternative design style is to use pass transistors. The following is an example of a multiplexer.

- Complementary transmission gates are used here because n-channel pass transistors will pass 0 logic level well but, 1 logic level poorly. This is because in order for the n-transistor to be **ON**, V<sub>gs</sub> must be greater than V<sub>th</sub>. Therefore each series n transistor will degrade the 1 logic level by V<sub>th</sub>. The opposite is true with p-channel pass transistors: 0 logic level is passed poorly.

### **Pass Transistor Logic with feedback**

This circuit uses only n transistors, therefore it is economical on transistor count. In order to ensure that the 1 logic level is passed properly, a p pull-up transistor is added. This restores the 1 logic level at the input of the inverter.

| PYKC 25-Jan-02 | E4.20 Digital IC Design | Lecture 6 - 37 | PYKC 25-Jan-02 |

|----------------|-------------------------|----------------|----------------|

|                |                         |                |                |

|                |                         |                |                |

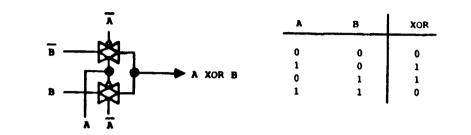

### **Pass Transistor XOR gate**

Pass transistor logic can sometimes be very economical in implementing logic functions. For example, an **XOR** gate can be implemented with just two transmission gates:-

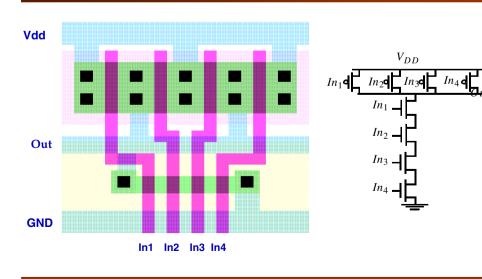

### 4-input NAND Gate

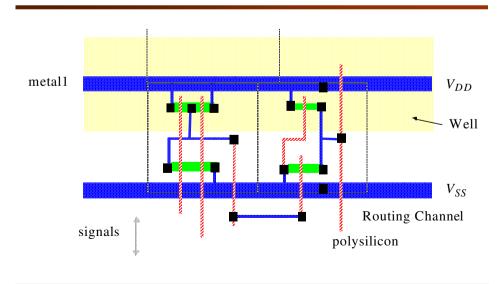

#### **Standard Cell Layout Methodology**