### **Recent development in PTL**

• New development by designers at Hitachi Japan

► Complementary Pass-transistor Logic (CPL), 1990

► Lean Integration with Pass-transistors (LEAP), 1996

• All exploit pass-transistors to implement general

► Double Pass-transistor Logic (DPL), 1993

in the last 6 years.

logic functions

• Three circuit styles proposed:

### Lecture 11 **Pass Transistor Logic**

Peter Cheuna Department of Electrical & Electronic Engineering Imperial College London

Reading "Top-Down Pass-Transistor Logic Design", K. Yano etc., IEEE J. of Solid-State Circuits, Vol 31, No. 6, June 1996.

> URL: www.ee.ic.ac.uk/pcheung/ E-mail: p.cheung@ic.ac.uk

| 22-Feb-02 | E4.20 Digital IC Design | Lecture 11 - 1 | 22-Feb-02 |  |

|-----------|-------------------------|----------------|-----------|--|

|           | g                       |                |           |  |

#### E4.20 Digital IC Design

Lecture 11 - 2

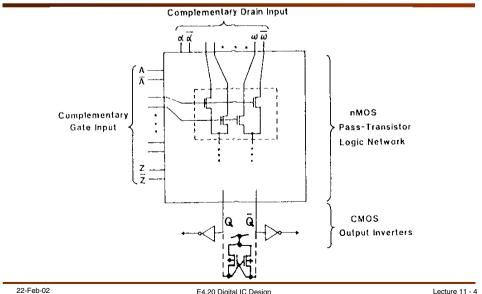

# **Complementary Pass-transistor Logic (CPL)**

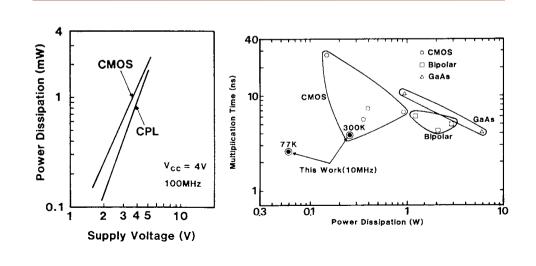

- "A 3.8 ns CMOS 16 x 16b Multiplier Using Complementary Pass-Transistor Logic" by K. Yano etc., IEEE J. of Solid-state Circuits, Vol 15, No 2, April 1990.

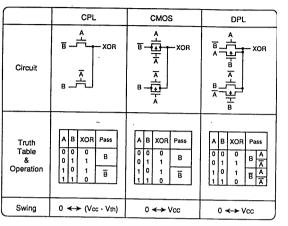

- Logic network employs input signals at both gate and drain terminals.

- Inputs and Outputs are always complementary.

- Outputs from network provide strong '0's but weak '1's. Inverters and PMOS pull-ups provide amplification and buffering as necessary.

# **Complementary Pass-transistor Logic (CPL)**

Lecture 11 - 3

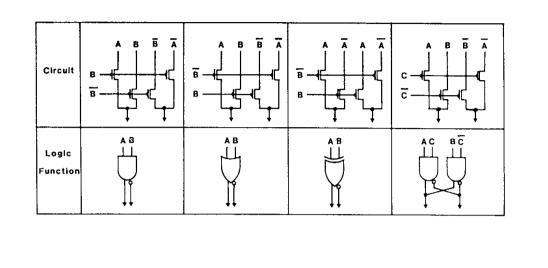

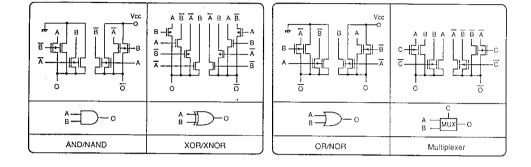

## **Basic gates designed in CPL**

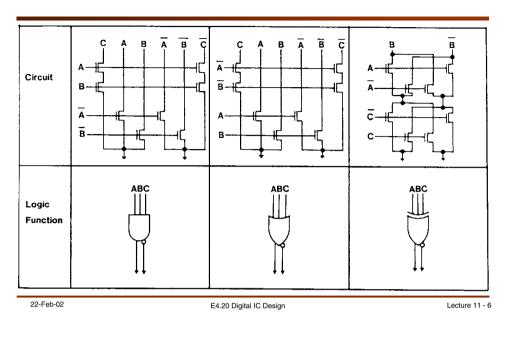

## 3-input gates designed in CPL

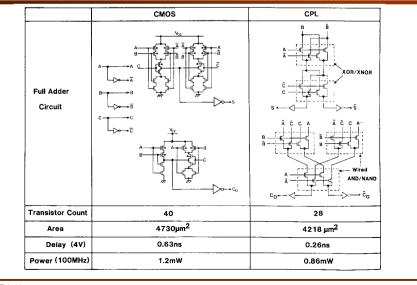

## CPL based 1-bit full adder

E4.20 Digital IC Design

## **Advantages of CPL**

22-Feb-02

Lecture 11 - 7

Lecture 11 - 5

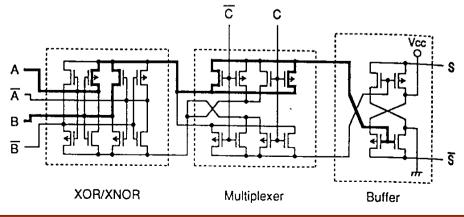

"A 1.5-ns 32-b CMOS ALU in Double Pass-Transistor Logic", M. Suzuki etc., IEEE J. of Solid-State Circuits, Vol 28, No 11, Nov., 1993

#### **Basic gates in DPL**

22-Feb-02

E4.20 Digital IC Design

Lecture 11 - 9

22-Feb-02

22-Feb-02

# Why is DPL faster?

|                      | CPL                          | CMOS        | DPL |

|----------------------|------------------------------|-------------|-----|

| Current<br>Path      | -> <sup>B</sup> - <u>3</u> W |             |     |

| Equiv.<br>Circuit    |                              |             |     |

| Equiv.<br>Resistance | <u>4</u> 3 R                 | 3<br>2<br>R | R   |

#### Sum circuit in DPL

E4.20 Digital IC Design

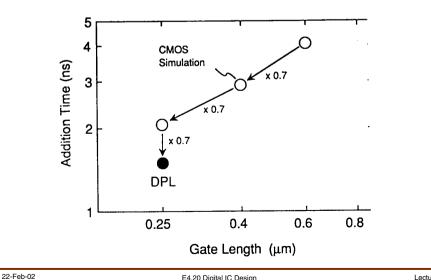

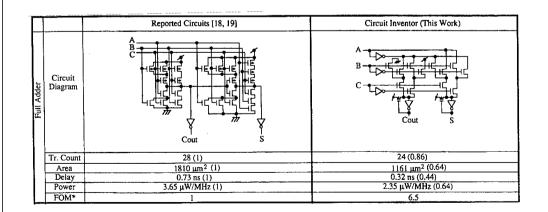

This adder circuit is extremely elegant. We have shown that for 0.6 micron technology, it offers up to 20% faster operating speed when compare with normal CMOS with only marginal increase in area.

Lecture 11 - 11

Lecture 11 - 10

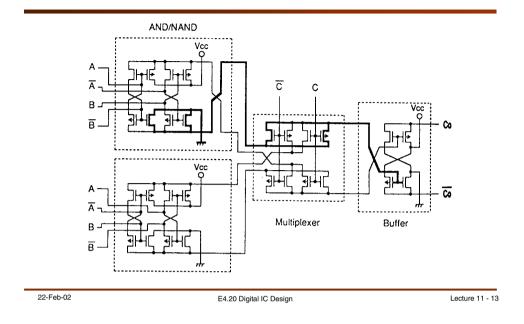

## **Carry circuit in DPL**

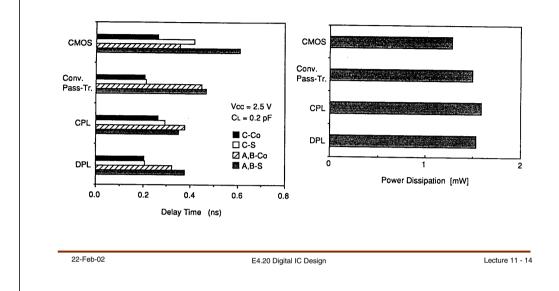

## **Power & Speed of DPL**

# **Overall add time of DPL**

# Lean Integration with Pass-Transistor (LEAP)

- "Top-Down Pass-Transistor Logic Design", K. Yano etc., IEEE J. of Solid-State Circuits, Vol 31, No. 6, June 1996.

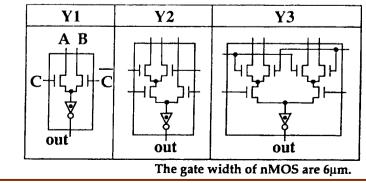

- It eliminated the need for keeping a large cell library by replacing a library of 61 basic cells with a new set of THREE library cells called Y1, Y2 and Y3, and 4 inverters of different drive strength.

Lecture 11 - 15

22-Feb-02

#### **Inverters used in LEAP**

• Note that the inverter on the left is used for driving very large output load and the right inverter for normal load capacitance.

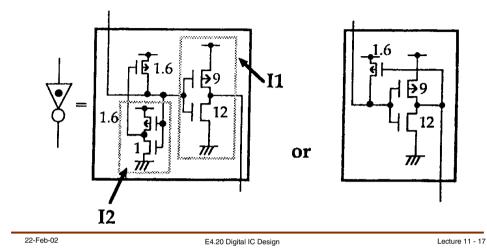

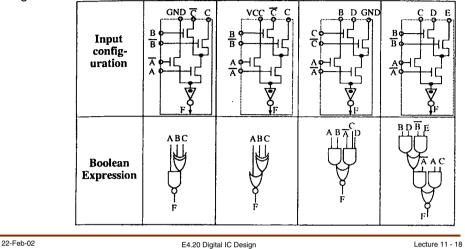

## Y2 can be configured for different logic

Arbitrary logic circuits can be implement at almost transistor level, not gate level.

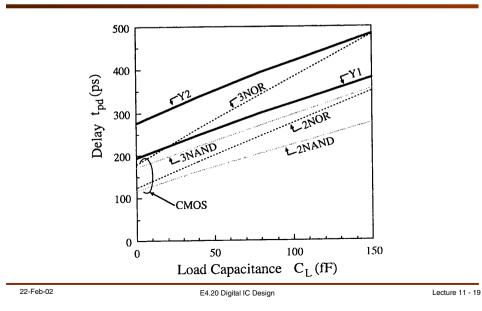

# Speed of LEAP

## **CMOS vs LEAP**

22-Feb-02