# **Topic 6**

# CMOS Static & Dynamic Logic Gates

Peter Cheung

Department of Electrical & Electronic Engineering

Imperial College London

URL: www.ee.ic.ac.uk/pcheung/ E-mail: p.cheung@ic.ac.uk

PYKC Nov-27-09 E4.20 Digital IC Design Topic 6 - 1

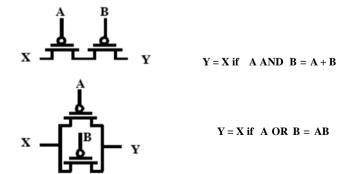

#### **PMOS Transistors in Series/Parallel Connection**

# PMOS switch closes when switch control input is low

PMOS Transistors pass a "strong" 1 but a "weak" 0

#### **NMOS Transistors in Series/Parallel Connection**

- ◆Transistors can be thought as a switch controlled by its gate signal

- ◆NMOS switch closes when switch control input is high

NMOS Transistors pass a "strong" 0 but a "weak" 1

PYKC Nov-27-09 E4.20 Digital IC Design Topic 6 - 2

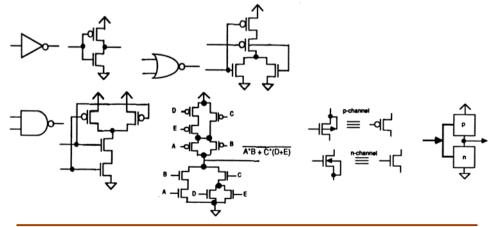

### **Static CMOS Circuit**

- Basic CMOS combinational circuits consist of:

- Complementary pull-up (p-type) and pull-down (n-type)

PYKC Nov-27-09 E4.20 Digital IC Design Topic 6 - 3 PYKC Nov-27-09 E4.20 Digital IC Design Topic 6 - 4

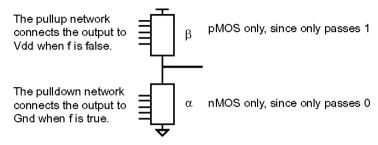

### **Static CMOS**

To build a logic gate  $\bar{f}(x_1, ..., x_n)$ , need to build two switch networks:

Pulldown

$$\alpha(x_1, ..., x_n) = f(x_1, ..., x_n)$$

Pullub

$$\beta(\overline{x}_1, \ldots, \overline{x}_n) = \overline{f}(x_1, \ldots, x_n)$$

(since pMOS invert inputs)

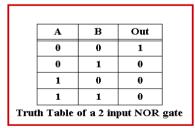

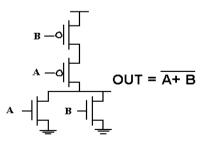

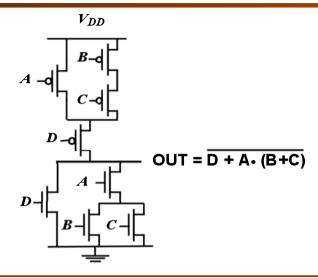

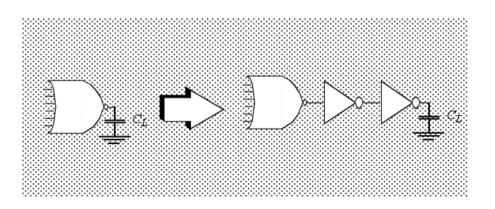

# **Example Gate: NOR**

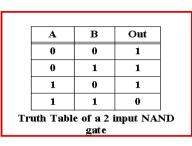

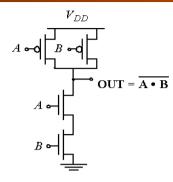

### **Example Gate: NAND**

PDN:

$$G = A B$$

$\Rightarrow$  Conduction to GND

PUN:  $F = A + B$   $= AB \Rightarrow$  Conduction to  $V_{DD}$

$$\overline{G(In_1,In_2,In_3,...)} \equiv F(\overline{In_1},\overline{In_2},\overline{In_3},...)$$

PYKC Nov-27-09 E4.20 Digital IC Design Topic 6 - 6

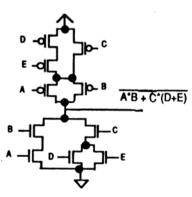

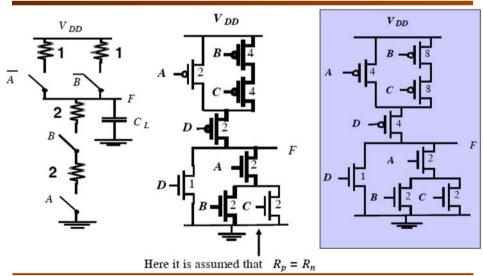

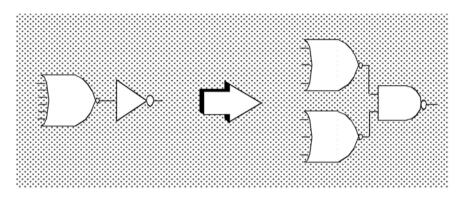

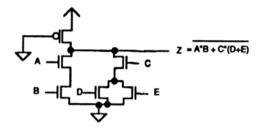

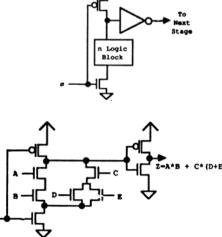

## **Complex Gate**

- We can form complex combinational circuit function in a complementary tree. The procedure to construct a complementary tree is as follow:-

- Express the boolean expression in an inverted form

- For the n-transistor tree, working from the inner -most bracket to the outer-most term, connect the OR term transistors in parallel, and the AND term transistors in series

- For the p-transistor tree, working from the inner -most bracket to the outer-most term, connect the OR term transistors in series, and the AND term transistors in parallel

### **Example Gate: COMPLEX CMOS GATE**

PYKC Nov-27-09 E4.20 Digital IC Design Topic 6 - 9

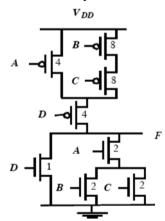

# **Transistor Sizing**

- for symmetrical response (dc, ac)

- for performance

# **Input Dependent**

Focus on worst-case

• assume  $\mu_n$ =2\*  $\mu_p$  (i.e. n-channel transistors has 2 times the transconductance as that of p -channel.)

### **Properties of Complementary CMOS Gates**

- 1) High noise margins  $V_{OH}$  and  $V_{OL}$  are at  $V_{DD}$  and GND, respectively.

- 2) No static power consumption There never exists a direct path between  $V_{DD}$  and  $V_{SS}(GND)$  in steady-state mode

- 3) Comparable rise and fall times: (under the appropriate scaling conditions)

PYKC Nov-27-09 E4.20 Digital IC Design Topic 6 - 10

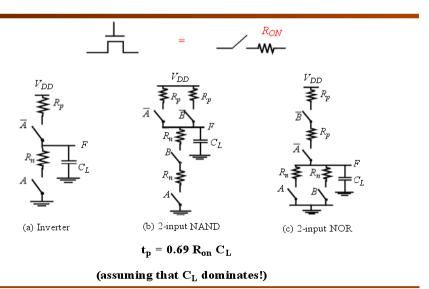

### **Propagation Delay Analysis - The Switch Model**

PYKC Nov-27-09 E4.20 Digital IC Design Topic 6 - 11 PYKC Nov-27-09 E4.20 Digital IC Design Topic 6 - 12

# What is the Value of $R_{on}$ ?

- Depends strongly on the operating region

- For hand analysis use a fixed value of R which it the average of the two end points of the transition

- Similar to the previous approach of averaging currents

### EXAMPLE: For $t_{DHL}$ for an inverter, the $R_{on}$ is:

$$R_{on} = \frac{1}{2} (R_{NMOS}(V_{out} = V_{DD}) + R_{NMOS}(V_{out} = V_{DD}/2))$$

$$= \frac{1}{2} \left( \left( \frac{V_{DS}}{I_D} \right)_{V_{out}} = V_{DD} + \left( \frac{V_{DS}}{I_D} \right)_{V_{out}} = V_{DD}/2 \right)$$

PYKC Nov-27-09 E4.20 Digital IC Design Topic 6 - 13

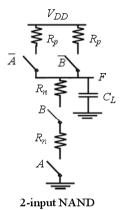

# **Design for Worst Case**

### **Analysis of Propagation Delay**

- 1. Assume  $R_n = R_p$  = resistance of minimum sized NMOS inverter

- 2. Determine "Worst Case Input" transition (Delay depends on input values)

- 3. Example:  $t_{pLH}$  for 2input NAND

- Worst case when only ONE PMOS Pulls up the output node

- For 2 PMOS devices in parallel, the resistance is lower

$$t_{pLH} = 0.69 R_p C_L$$

- 4. Example:  $t_{pHL}$  for 2input NAND

- Worst case: TWO NMOS in series

$$t_{pHL} = 0.69(2R_n)C_L$$

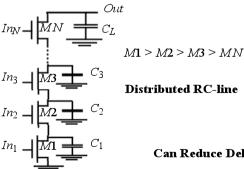

# **Fast Complex Gate - Design Techniques**

- Transistor Sizing:

- As long as Fan-out Capacitance dominates

- Progressive Sizing:

Can Reduce Delay with more than 30%!

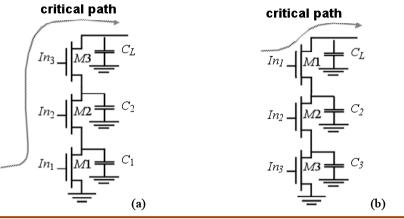

# **Fast Complex Gate - Design Techniques (2)**

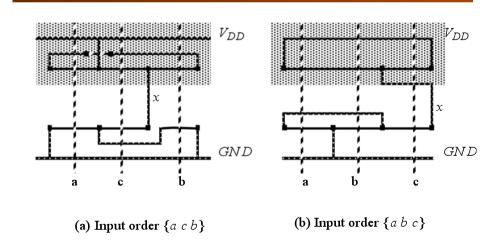

# Transistor Ordering

PYKC Nov-27-09 E4.20 Digital IC Design Topic 6 - 17

# Fast Complex Gate - Design Techniques (4)

# • Buffering: Isolate Fan-in from Fan-out

# Fast Complex Gate - Design Techniques (3)

# • Improved Logic Design

PYKC Nov-27-09 E4.20 Digital IC Design Topic 6 - 18

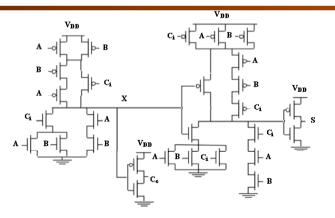

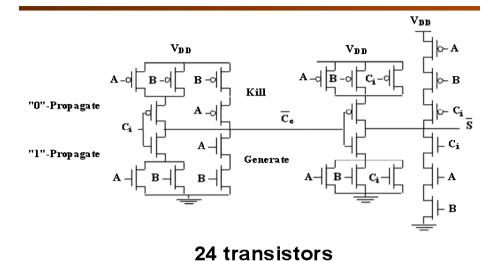

# **Example: Full Adder**

$C_0 = AB + C_i(A+B)$

28 transistors

PYKC Nov-27-09 E4.20 Digital IC Design Topic 6 - 19 PYKC Nov-27-09 E4.20 Digital IC Design Topic 6 - 20

#### **A Revised Adder Circuit**

PYKC Nov-27-09 E4.20 Digital IC Design Topic 6 - 21

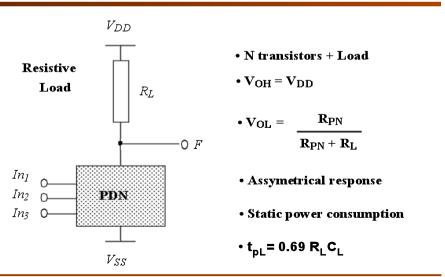

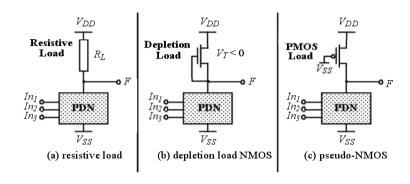

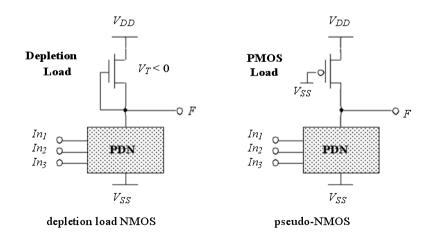

# **Ratioed Logic**

### **Ratioed Logic**

Goal: to reduce the number of devices over complementary CMOS

PYKC Nov-27-09 E4.20 Digital IC Design Topic 6 - 22

### **Active Loads**

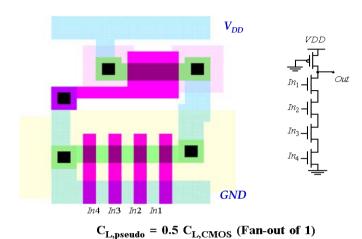

### **Psuedo NMOS**

- Disadvantages of previous circuit:

- Almost twice as many transistors as equivalent NMOS implementation.

- If there are too many series transistors in the tree, switching speed is reduced.

- ◆ Try a pseudo NMOS circuit:-

- The pull-up p-channel transistor is always conducting.

- Disadvantages: high d.c. dissipation & slow rise time.

# **Improved Loads (1)**

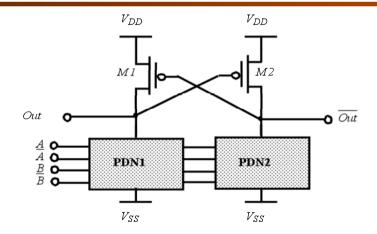

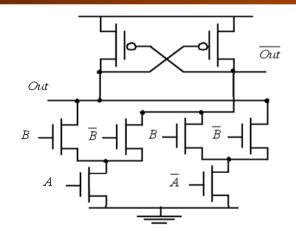

### Dual Cascode Voltage Switch Logic (DCVSL)

### **Pseudo-NMOS NAND Gate**

PYKC Nov-27-09 E4.20 Digital IC Design Topic 6 - 26

#### Example

#### XOR-NXOR gate

PYKC Nov-27-09 E4.20 Digital IC Design Topic 6 - 27 PYKC Nov-27-09 E4.20 Digital IC Design Topic 6 - 28

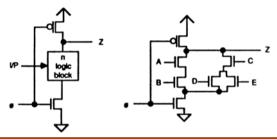

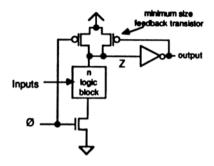

### **Dynamic Logic**

- There is another class of logic gates which relies on the use of a clock signal. This class of circuit is known as dynamic circuits. The clock signal is used to divide the gate operation into two halves. In the first half, the output node is pre-charged to a high or low logic state. In the second half of a clock cycle, the circuit evaluates the correct output state.

- When Ø is low, Z is charged to high. When Ø is high, n logic block evaluates input, and conditionally discharges Z. This circuit adds series resistance to the pull-down n-channel transistor, therefore the fall time is increased slightly.

- This circuit is dynamic because during evaluation, the output high level at Z is maintained by the stray capacitance at the output node. If Ø stays high (i.e. evaluation period) for a long time, Z may eventually discharge to a low logic level.

## **CMOS Domino Logic**

- Solution to the above problem:-

- Add an inverter to ensure that the output is low during precharge, and prevent the next stage from evaluating, until the current stage has finished evaluation.

- This ensures that each stage (at the output of the inverter) will make at most a single transition from 0 -> 1.

- When many stages are cascaded, evaluation proceeds from one stage to the next - similar to dominos falling one after another.

- Disadvantages of domino logic:-

- Only non-inverting logic is possible, i.e. output also high active

- Each gate needs an inverter; hence more transistors

- Suffer from charge sharing effect (considered later)

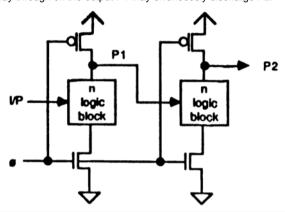

### **Problem with Cascading Dynamic Logic**

- Problem with cascading such as a circuit:-

- Inputs can only be changed when Ø is low and must be stable when Ø is high.

- When Ø is low, both P1 and P2 are precharged to a high voltage. However when Ø is high, delay through on the output P1 may erroneously discharge P2.

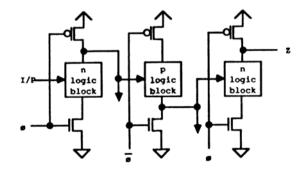

### **Alternating dynamic logic (1)**

- Another possible scheme is to use alternate n and p logic blocks as shown below.

- In this scheme, each alternate stage is pre-charged high and low. Each stage uses alternate n and p transistors to implement the gate function. Stage 1 makes at most one high to low transition, while stage 2 makes at most one low to high transition for each evaluation. Since the p logic block will only change state if input is a low, this circuit behaves like the domino logic.

PYKC Nov-27-09 E4.20 Digital IC Design Topic 6 - 31 PYKC Nov-27-09 E4.20 Digital IC Design Topic 6 - 32

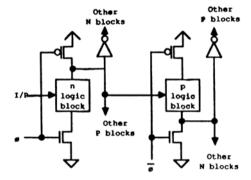

# **Alternating dynamic logic (2)**

A slight variation of this circuit is show below, where an inverter is added per stage to increase flexibility. Here each stage can drive either n or p blocks and both low active and high active logic can be implemented.

PYKC Nov-27-09 E4.20 Digital IC Design Topic 6 - 33

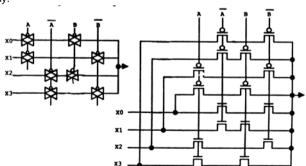

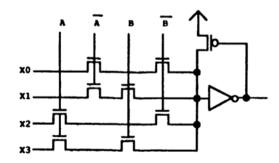

# **Pass Transistor Logic**

- An alternative design style is to use pass transistors. The following is an example of a multiplexer.

- Complementary transmission gates are used here because n-channel pass transistors will pass 0 logic level well but, 1 logic level poorly. This is because in order for the n-transistor to be ON, V<sub>gs</sub> must be greater than V<sub>th</sub>. Therefore each series n transistor will degrade the 1 logic level by V<sub>th</sub>. The opposite is true with p-channel pass transistors: 0 logic level is passed poorly.

### **Making a Dynamic Gate static**

- Finally, by adding a feedback pullup, we can make the circuit static.

- This circuit turns the originally dynamic gate into a static gate because the feedback transistor can maintain a logic high level at the node Z for an indefinite length of time.

Without this feedback transistor, the charge stored at the node Z will eventually leak away.

### Pass Transistor Logic with feedback

This circuit uses only n transistors, therefore it is economical on transistor count. In order to ensure that the 1 logic level is passed properly, a p pull-up transistor is added. This restores the 1 logic level at the input of the inverter.

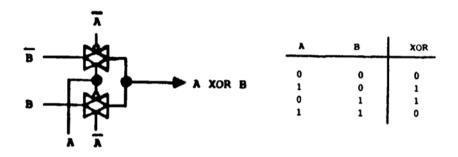

# **Pass Transistor XOR gate**

Pass transistor logic can sometimes be very economical in implementing logic functions. For example, an XOR gate can be implemented with just two transmission gates:-

PYKC Nov-27-09 E4.20 Digital IC Design Topic 6 - 37

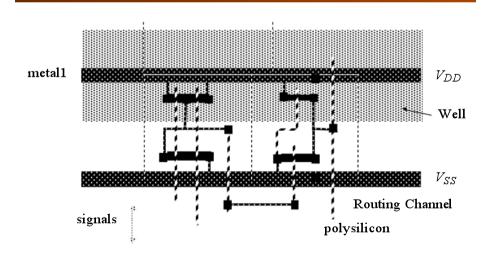

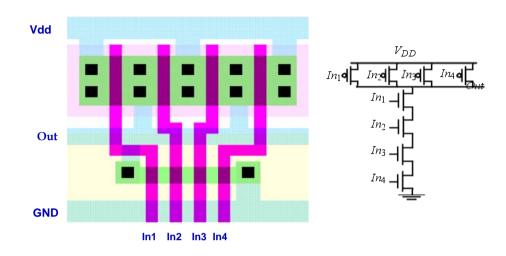

# **Standard Cell Layout Methodology**

# 4-input NAND Gate

# Two Versions of (a+b).c

PYKC Nov-27-09 E4.20 Digital IC Design Topic 6 - 39 PYKC Nov-27-09 E4.20 Digital IC Design Topic 6 - 40