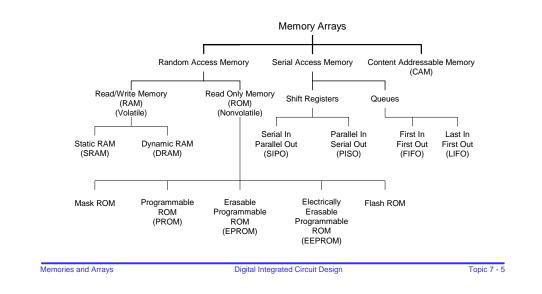

# **Memory Arrays**

### **Outline**

- Memory classification

- Basic building blocks ٠

- ROM ٠

- Non Volatile Read Write Memories

- Static RAM (SRAM) ٠

- Dynamic RAM (DRAM) ٠

- Memory peripheral circuit

- Content Addressable Memory (CAM) ٠

- Serial access memories ٠

- Programmable Logic Array ٠

- Reliability and Yield ٠

- Memory trends

Memories and Arrays

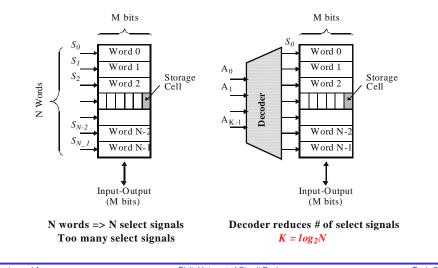

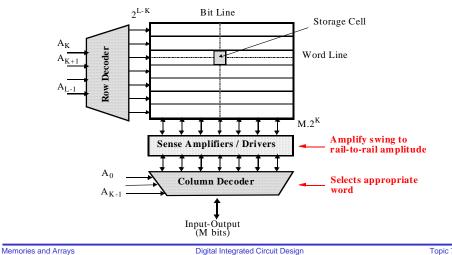

**Memory Architecture: Decoders**

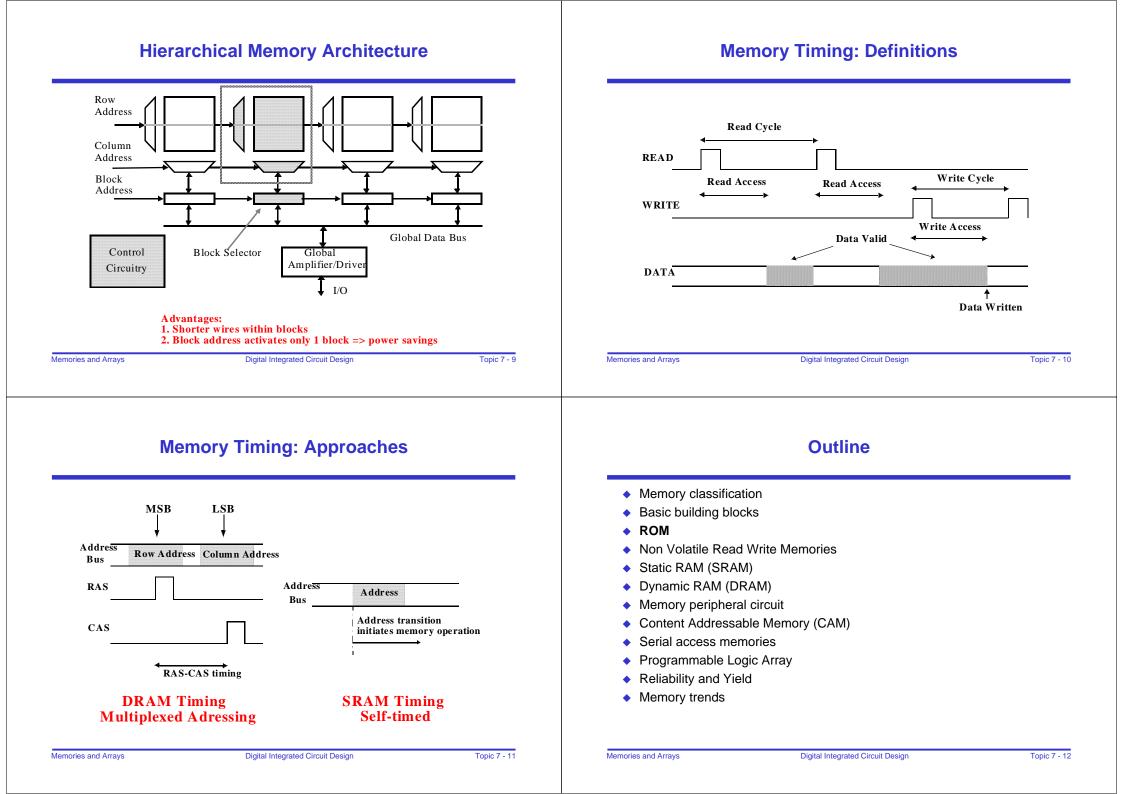

# **Array-Structured Memory Architecture**

Digital Integrated Circuit Design

#### Problem: ASPECT RATIO or HEIGHT >> WIDTH

Memories and Arrays

Topic 7 - 8

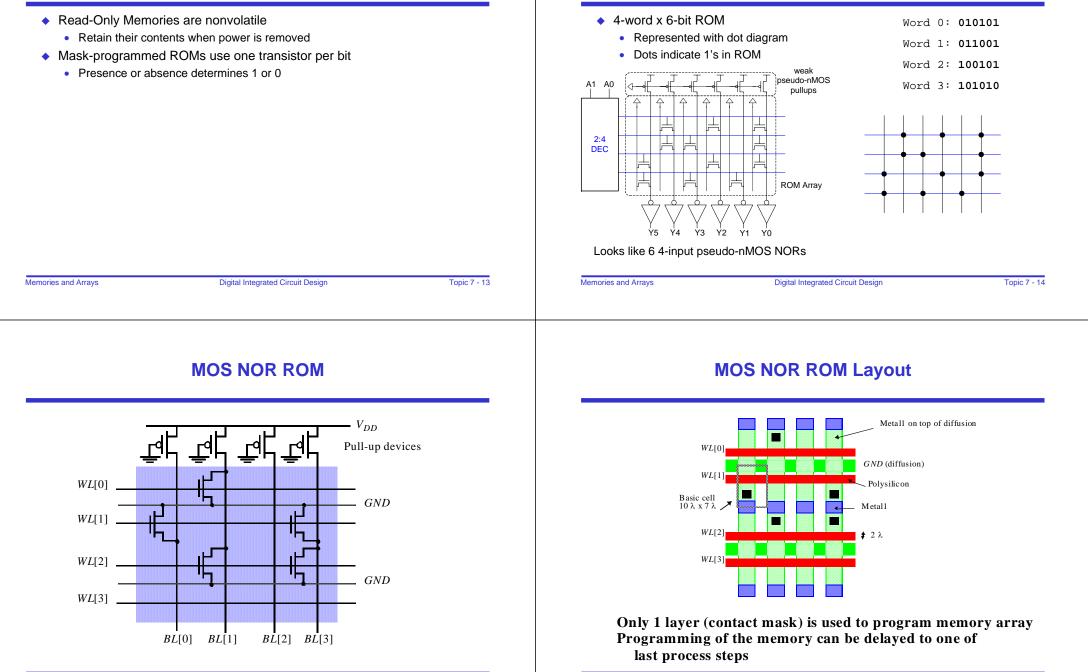

# **Read-Only Memories**

**ROM Example**

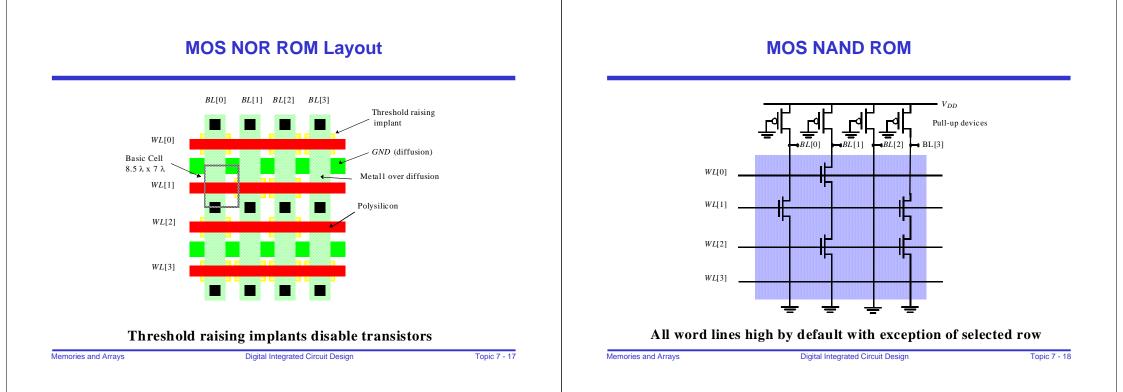

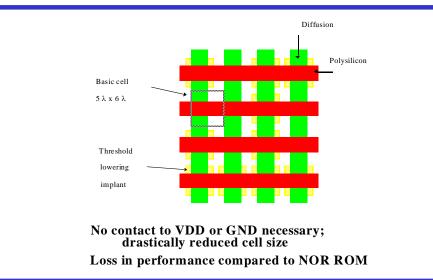

# **MOS NAND ROM Layout**

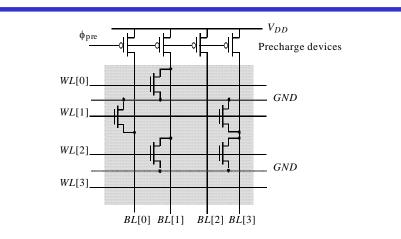

# Precharged MOS NOR ROM

PMOS precharge device can be made as large as necessary, but clock driver becomes harder to design.

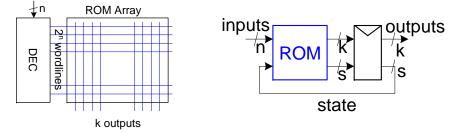

# **Building Logic with ROMs**

**Outline**

- Use ROM as lookup table containing truth table

- n inputs, k outputs requires 2<sup>n</sup> words x k bits

- Changing function is easy reprogram ROM

- Finite State Machine

- n inputs, k outputs, s bits of state

- Build with 2<sup>n+s</sup> x (k+s) bit ROM and (k+s) bit reg

#### inputs

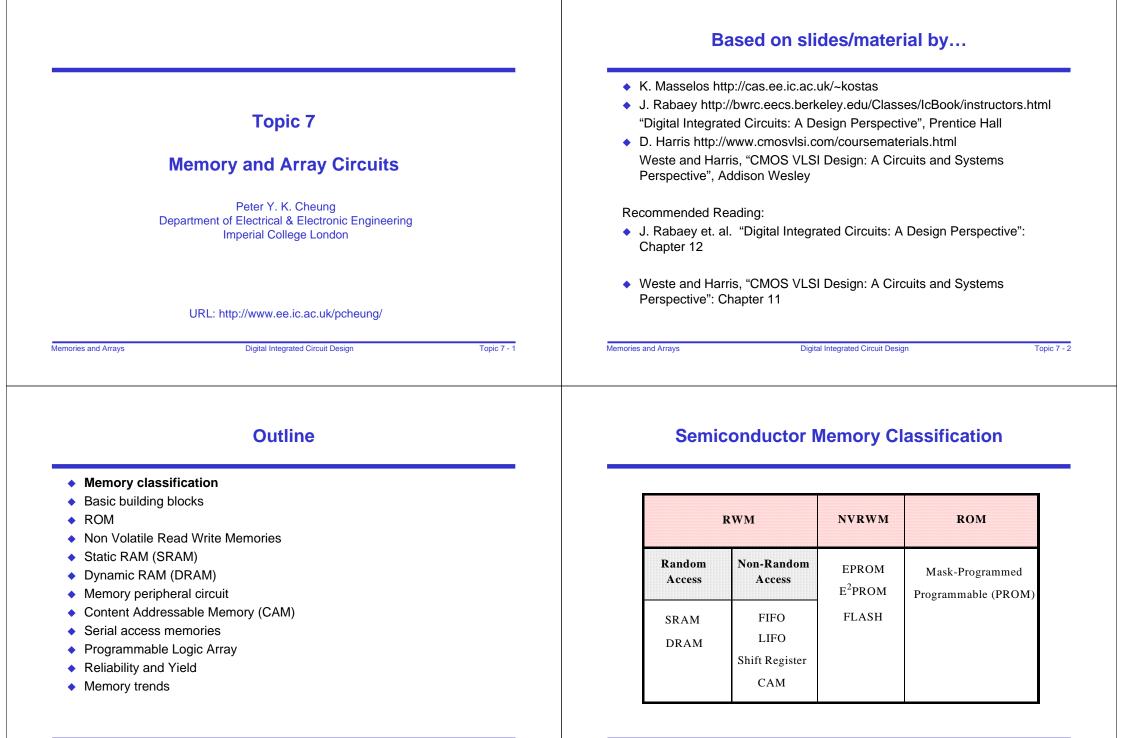

#### Memory classification

- Basic building blocks

- ROM

- Non Volatile Read Write Memories

- Static RAM (SRAM)

- Dynamic RAM (DRAM)

- Memory peripheral circuit

- Content Addressable Memory (CAM)

- Serial access memories

- Programmable Logic Array

- Reliability and Yield

- Memory trends

#### Memories and Arrays

Digital Integrated Circuit Design

Memories and Arrays

Digital Integrated Circuit Design

Topic 7 - 22

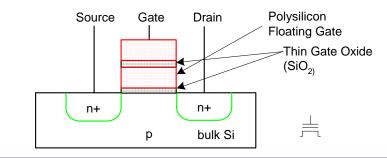

# Nonvolatile Read-Write Memories (NVRW)

- Architecture virtually identical to the ROM structure

- the memory core consists of an array of transistors placed on a word-line/bitline grid

- The memory is programmed by selectively disabling or enabling some of those devices

- in a ROM this is accomplished by mask level alterations

- in a NVRW memory a modified transistor that permits its threshold to be altered electrically is used instead – the modified threshold is retained indefinitely (or long) even when the supply voltage is turned off

- To reprogram the memory the programmed values must be erased after which a new programming round can be started

- The method of erasing is the main differentiating factor between the various classes of reprogrammable non volatile memories

- The programming of the memory is typically an order of magnitude slower than the reading operation

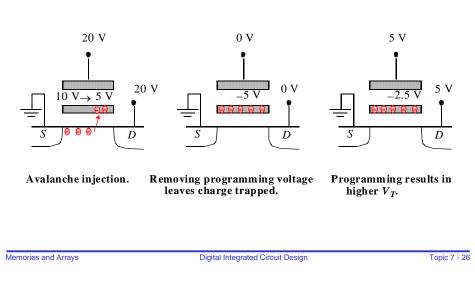

### **PROMs and EPROMs**

- Programmable ROMs

- Build array with transistors at every site

- Burn out fuses to disable unwanted transistors

- Electrically Programmable ROMs

- Use floating gate to turn off unwanted transistors

- EPROM, EEPROM, Flash

Topic 7 - 21

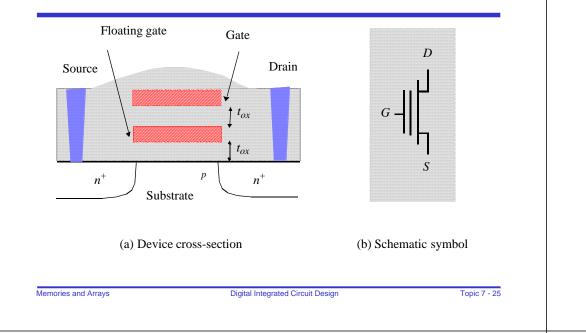

# Floating-gate transistor (FAMOS)

# **Floating-Gate Transistor Programming**

## **Characteristics of Non Volatile Memories**

|                                      | EPROM<br>[Tomita91]             | EEPROM<br>[Terada89,<br>Pashley89] | Flash EEPROM<br>[Jinbo92]        |  |

|--------------------------------------|---------------------------------|------------------------------------|----------------------------------|--|

| Memory size                          | 16 Mbit (0.6 μm)                | 1 Mbit (0.8<br>μm)                 | 16 Mbit (0.6 μm)                 |  |

| Chip size                            | 7.18 x 17.39<br>mm <sup>2</sup> | 11.8 x 7.7<br>mm <sup>2</sup>      | 6.3 x 18.5 mm <sup>2</sup>       |  |

| Cell size                            | $3.8 \ \mu m^2$                 | $30 \ \mu m^2$                     | $3.4 \ \mu m^2$                  |  |

| Access time                          | 62 nsec                         | 120 nsec                           | 58 nsec                          |  |

| Erasure time                         | minutes                         | N.A.                               | 4 sec                            |  |

| Programming<br>time/word             | 5 µsec                          | 8 msec/word,<br>4 sec /chip        | 5 μsec                           |  |

| Erase/Write<br>cycles<br>[Pashley89] | 100                             | 10 <sup>5</sup>                    | 10 <sup>3</sup> -10 <sup>5</sup> |  |

### Outline

- Memory classification

- Basic building blocks

- ROM

- Non Volatile Read Write Memories

- Static RAM (SRAM)

- Dynamic RAM (DRAM)

- Memory peripheral circuit

- Content Addressable Memory (CAM)

- Serial access memories

- Programmable Logic Array

- Reliability and Yield

- Memory trends

# **Read-Write Memories (RAM)**

Data stored as long as supply is applied

Large (6 transistors/cell)

**Periodic refresh required**

Small (1-3 transistors/cell)

• STATIC (SRAM)

Fast

Differential

DYNAMIC (DRAM)

Slower

Single Ended

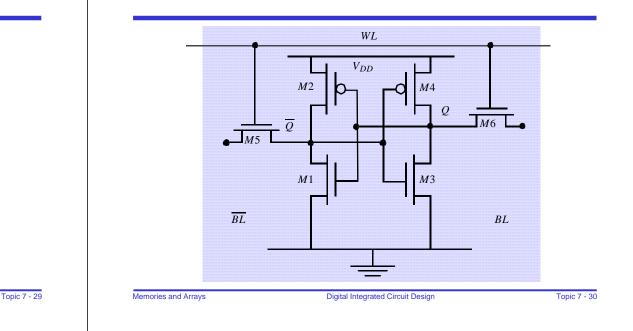

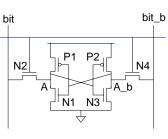

### 6-transistor CMOS SRAM Cell

# **SRAM Read/Write**

Digital Integrated Circuit Design

The key issue in an 6T SRAM is how to distinguish between read and writes. There is only one wordline, so it must be high for both reads and writes. The key is to use the fact there are two bitlines.

#### Read:

Memories and Arrays

• Both Bit and Bit must start high. A high value on the bitline does not change the value in the cell, so the cell will pulls one of the lines low

#### Write:

- One (Bit or Bit) is forced low, the other is high

- This low value overpowers the pMOS in the inverter, and this will write the cell.

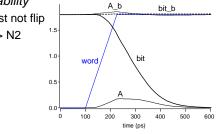

# **CMOS SRAM Analysis (Read)**

- Precharge both bitlines high

- Then turn on wordline

- One of the two bitlines will be pulled down by the cell word

- ◆ Ex: A = 0, A b = 1

- bit discharges, bit\_b stays high

- But A bumps up slightly

- Read stability

- A must not flip

- N1 >> N2

Memories and Arrays

Topic 7 - 31

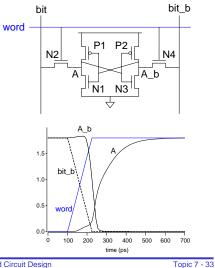

# **CMOS SRAM Analysis (Write)**

- Drive one bitline high, the other low

- Then turn on wordline

- Bitlines overpower cell with new value

- Ex: A = 0, A\_b = 1, bit = 1, bit\_b = 0

- Force A\_b low, then A rises high

- Writability

- Must overpower feedback inverter

- N2 >> P1

| Memories and Arrays | Digital Integrated Circuit Design |  |  |

|---------------------|-----------------------------------|--|--|

|                     |                                   |  |  |

|                     |                                   |  |  |

|                     |                                   |  |  |

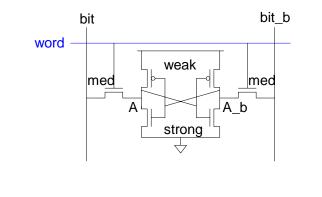

# SRAM Sizing

- High bitlines must not overpower inverters during reads

- But low bitlines must write new value into cell

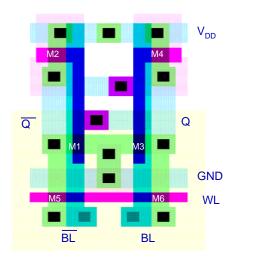

6T-SRAM — Layout

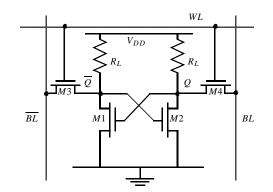

# **Resistance-load SRAM Cell**

Digital Integrated Circuit Design

Static power dissipation -- Want  $R_L$  large Bit lines precharged to  $V_{DD}$  to address  $t_p$  problem

Memories and Arrays

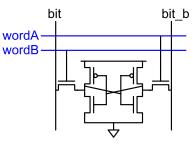

# **Multiple Ports**

# **Dual-Ported SRAM**

- We have considered single-ported SRAM

One read or one write on each cycle

Multiported SRAM are needed for register files

- Examples:

- Multicycle MIPS must read two sources or write a result on some cycles

- Pipelined MIPS must read two sources and write a third result each cycle

- Superscalar MIPS must read and write many sources and results each cycle

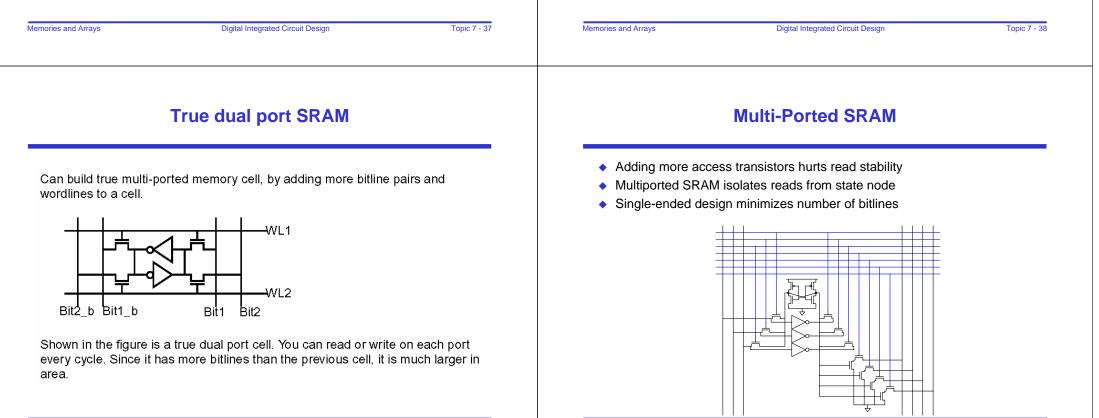

- Simple dual-ported SRAM

- Two independent single-ended reads

- Or one differential write

- Do two reads and one write by time multiplexing

- Read during ph1, write during ph2

### Outline

- Memory classification

- Basic building blocks

- ROM

- Non Volatile Read Write Memories

- Static RAM (SRAM)

- Dynamic RAM (DRAM)

- Memory peripheral circuit

- Content Addressable Memory (CAM)

- Serial access memories

- Programmable Logic Array

- Reliability and Yield

- Memory trends

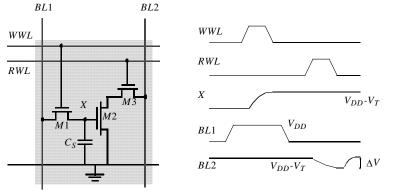

No constraints on device ratios Reads are non-destructive Value stored at node X when writing a "1" =  $V_{WWL}$ - $V_{Tn}$

| Memories and Arrays | Digital Integrated Circuit Design | Topic 7 - 41 | Memories and Arrays                      | Digital Integrated Circuit Design                                                                                                                                                  | Topic 7 - 4 |

|---------------------|-----------------------------------|--------------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

|                     | 3T-DRAM — Layout                  |              | ,                                        | 1-Transistor DRAM Cell                                                                                                                                                             |             |

|                     |                                   |              | $BL$ $WL$ $M1$ $C_{BL}$ $U$ $W$ $C_{BL}$ | $BL$ $V_{DD}/2$ sensitive or discharged by asserting WL and BL.                                                                                                                    | $V_{DD}/2$  |

|                     |                                   |              | Δ                                        | ibution takes places between bit line and storage c<br>$\Delta V = V_{BL} - V_{PRE} = (V_{BIT} - V_{PRE}) \frac{C_S}{C_S + C_{BL}}$<br>ge swing is small; typically around 250 mV. | араснансе   |

Topic 7 - 43

Memories and Arrays

- 42

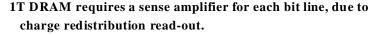

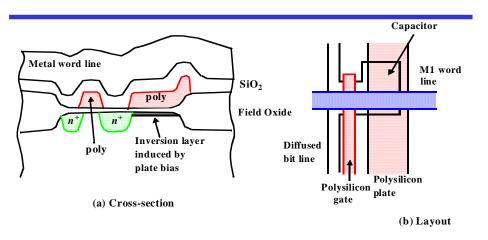

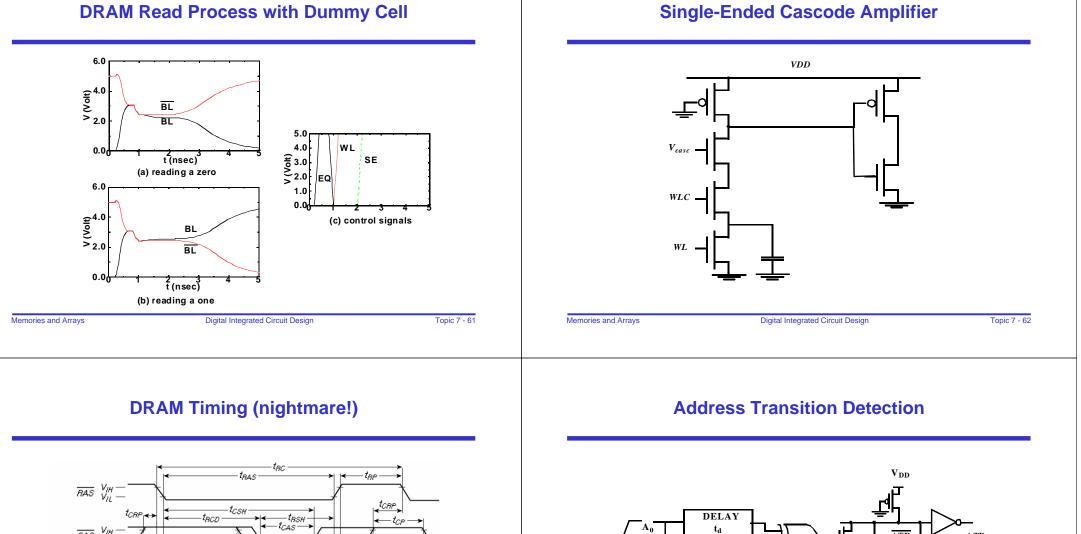

### **DRAM Cell Observations**

**1-T DRAM Cell**

- DRAM memory cells are single ended in contrast to SRAM cells.

- The read-out of the 1T DRAM cell is destructive; read and refresh operations are necessary for correct operation.

- Unlike 3T cell, 1T cell requires presence of an extra capacitance that must be explicitly included in the design.

- When writing a "1" into a DRAM cell, a threshold voltage is lost. This charge loss can be circumvented by bootstrapping the word lines to a higher value than  $V_{DD}$ .

#### **Used Polysilicon-Diffusion Capacitance**

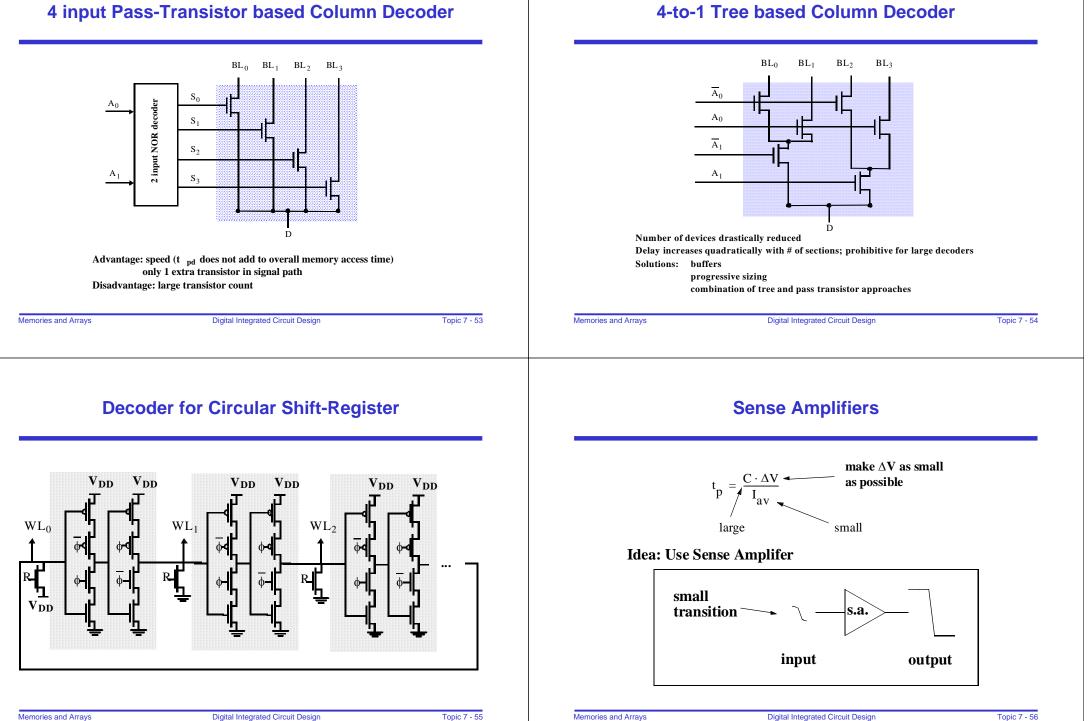

#### Periphery **Row Decoders** Decoders Collection of 2<sup>M</sup> complex logic gates Organized in regular and dense fashion Sense amplifiers (N)AND Decoder $WL_0 = A_0 A_1 A_2 A_3 A_4 A_5 A_6 A_7 A_8 A_9$ Input/output buffers $WL_{511} = A_0A_1A_2A_3A_4A_5A_6A_7A_8A_9$ Control/timing circuit **NOR Decoder** $WL_0 = \overline{A_0 + A_1 + A_2 + A_3 + A_4 + A_5 + A_6 + A_7 + A_8 + A_9}$ $WL_{511} = A_0 + \bar{A}_1 + \bar{A}_2 + \bar{A}_3 + \bar{A}_4 + \bar{A}_5 + \bar{A}_6 + \bar{A}_7 + \bar{A}_8 + \bar{A}_9$ Memories and Arrays Digital Integrated Circuit Design Topic 7 - 49 Memories and Arrays Digital Integrated Circuit Design Topic 7 - 50 A NAND Decoder using 2-input Pre-Decoders **Dynamic Decoders** Precharge devices GND GND VDD Ĩ, - WL<sub>1</sub> $WL_3$ WL<sub>2</sub> $V_{DD}$ Ŀ $WL_2$ WL<sub>2</sub> WL<sub>0</sub> $V_{DD}$ Ĩ $WL_1$ $WL_1$ $V_{DD}$ Űþ. $A_0\overline{A}_1 \overline{A}_0A_1 A_0A_1$ $\overline{A_2}\overline{A_3}$ $\overline{A_2}\overline{A_3}$ $\overline{A_2}\overline{A_3}$ $\overline{A_2}A_3$ $\overline{A_2}A_3$ A<sub>0</sub>A WLo • • • Ā $A_0$ $A_1$ **Dynamic 2-to-4 NOR decoder** 2-to-4 MOS dynamic NAND Decoder A<sub>1</sub> A<sub>3</sub> A<sub>2</sub> A<sub>2</sub> A<sub>3</sub> A<sub>0</sub> A<sub>1</sub> A<sub>0</sub>

Splitting decoder into two or more logic layers produces a faster and cheaper implementation

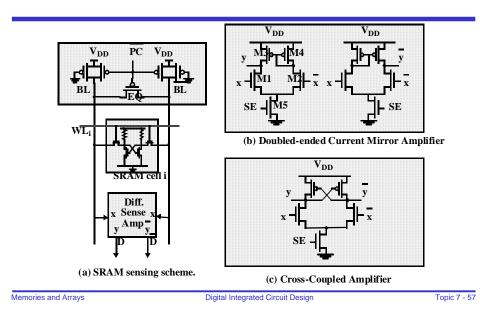

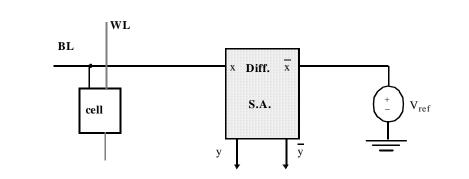

# **Differential Sensing - SRAM**

# **Single-to-Differential Conversion**

How to make good V<sub>ref</sub>?

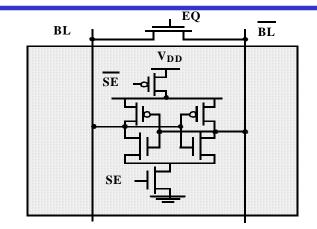

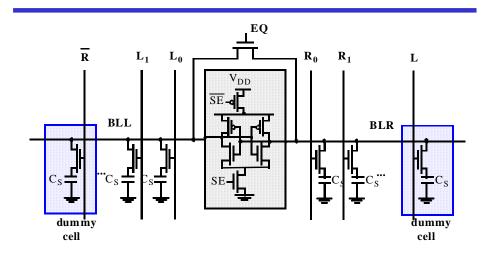

Initialized in its meta-stable point with EQ Once adequate voltage gap created, sense amp enabled with SE Positive feedback quickly forces output to a stable operating point.

# Memories and Arrays Digital Integrated Circuit Design Topic 7 - 58

### **Open Bitline Architecture**

#### Memories and Arrays

A<sub>1</sub>

A<sub>N-1</sub>

DELAY

td

DELAY

t<sub>d</sub>

ATD

ATD

Memories and Arrays

### Outline

- Memory classification

- Basic building blocks

- ROM

- Non Volatile Read Write Memories

- Static RAM (SRAM)

- Dynamic RAM (DRAM)

- Memory peripheral circuit

- Content Addressable Memory (CAM)

- Serial access memories

- Programmable Logic Array

- Reliability and Yield

- Memory trends

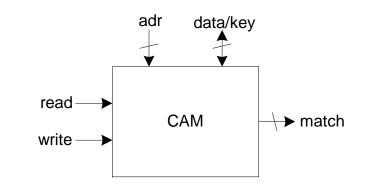

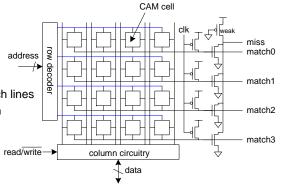

- Extension of ordinary memory (e.g. SRAM)

- Read and write memory as usual

- Also match to see which words contain a key

| Memories and Arrays | Digital Integrated Circuit Design | Topic 7 - 65 | Memories and Arrays | Digital Integrated Circuit Design | Topic 7 - 66 |

|---------------------|-----------------------------------|--------------|---------------------|-----------------------------------|--------------|

|                     |                                   |              |                     |                                   |              |

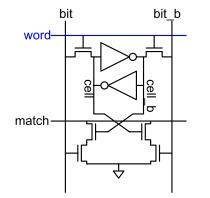

# **CAM Cell Operation**

- Read and write like ordinary SRAM

- For matching:

- Leave wordline low

- Precharge matchlines

- Place key on bitlines

- Matchlines evaluate

- Miss line

- Pseudo-nMOS NOR of match lines

- Goes high if no words match

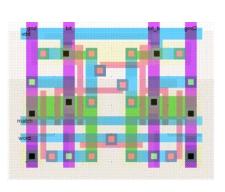

# **10T CAM Cell**

Add four match transistors to 6T SRAM

### Outline

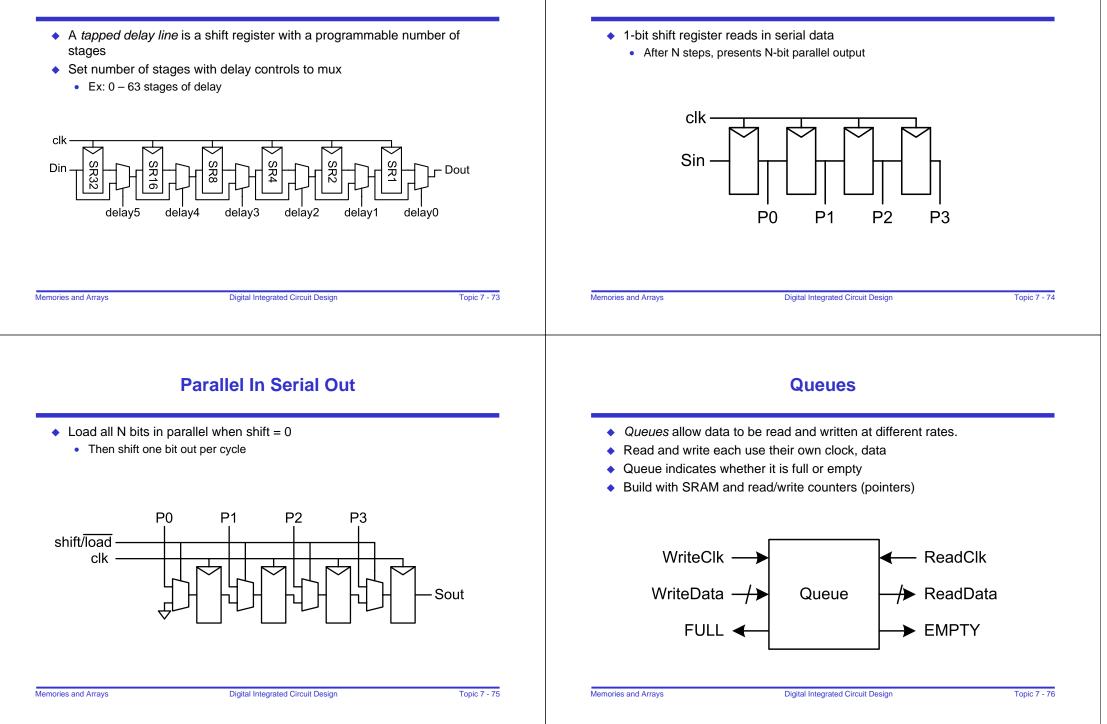

### **Serial Access Memories**

Memory classification Serial access memories do not use an address Basic building blocks Shift Registers ٠ Tapped Delay Lines ROM • Serial In Parallel Out (SIPO) Non Volatile Read Write Memories Parallel In Serial Out (PISO) Static RAM (SRAM) • Queues (FIFO, LIFO) Dynamic RAM (DRAM) • Memory peripheral circuit Content Addressable Memory (CAM) Serial access memories ٠ Programmable Logic Array ٠ Reliability and Yield Memory trends Memories and Arrays Digital Integrated Circuit Design Topic 7 - 69 Memories and Arrays Digital Integrated Circuit Design Topic 7 - 70 **Shift Register Denser Shift Registers** • Shift registers store and delay data Flip-flops aren't very area-efficient • Simple design: cascade of registers • For large shift registers, keep data in SRAM instead Watch your hold times! Move read/write pointers to RAM rather than data · Initialize read address to first entry, write to last • Increment address on each cycle Din clk clk counter readaddr 00...00 dual-ported counter SRAM Din Dout writeaddr 11...11 ᅷ reset Dout Memories and Arrays Digital Integrated Circuit Design Topic 7 - 71 Memories and Arrays Digital Integrated Circuit Design Topic 7 - 72

# **Tapped Delay Line**

**Serial In Parallel Out**

# **FIFO, LIFO Queues**

### Outline

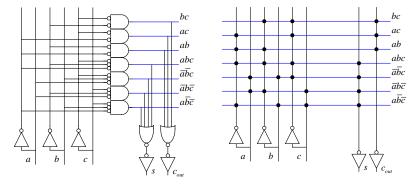

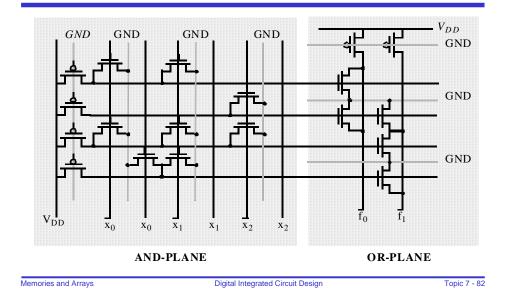

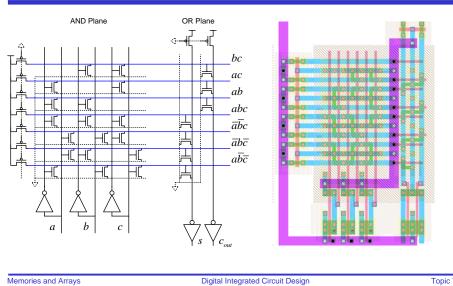

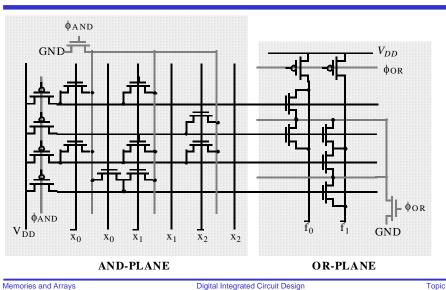

# **NOR-NOR PLAs**

- ANDs and ORs are not very efficient in CMOS

- Dynamic or Pseudo-nMOS NORs are very efficient

- Use DeMorgan's Law to convert to all NORs

# **Pseudo-Static PLA**

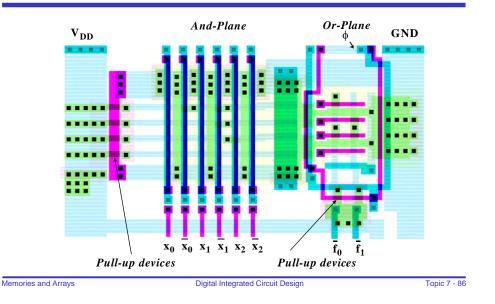

# **PLA Schematic & Layout**

Topic 7 - 83

Topic 7 - 81

OR

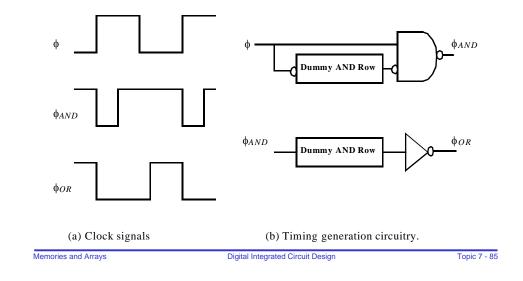

# **Clock Signal Generation for self-timed dynamic PLA**

# **PLA Layout**

# PLA versus ROM

Programmable Logic Array structured approach to random logic "two level logic implementation" NOR-NOR (product of sums) NAND-NAND (sum of products)

#### **IDENTICAL TO ROM!**

Main difference ROM: fully populated PLA: one element per minterm

#### Note: Importance of PLA's has drastically reduced

- 1. slow

- 2. better software techniques (mutli-level logic synthesis)

### Outline

- Memory classification

- Basic building blocks

- ROM

- Non Volatile Read Write Memories

- Static RAM (SRAM)

- Dynamic RAM (DRAM)

- Memory peripheral circuit

- Serial access memories

- Content Addressable Memory (CAM)

- Programmable Logic Array

- Reliability and Yield

- Memory trends

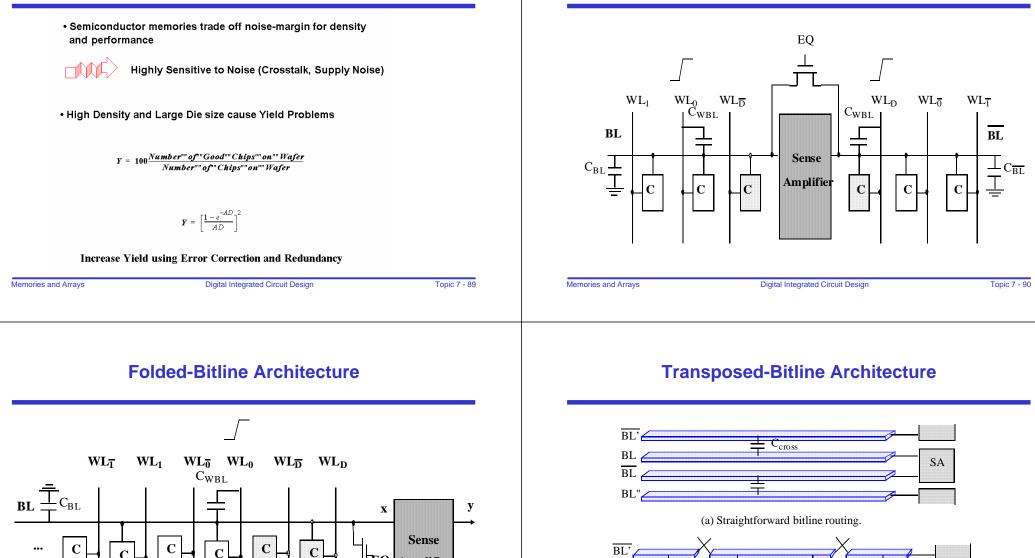

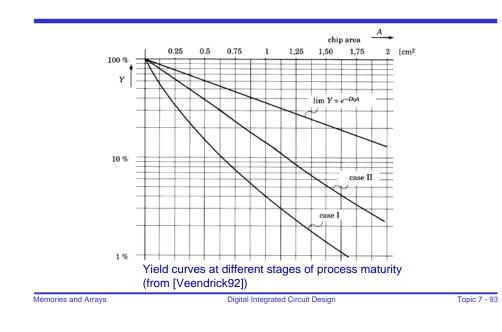

# **Reliability and Yield**

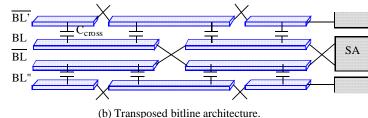

**Open Bit-line Architecture — Cross Coupling**

$\overline{\mathbf{BL}} \stackrel{\perp}{\underline{\top}} C_{\overline{\mathbf{BL}}}$

С

С

$C_{WBL}$

Topic 7 - 91

\_

v

EQ Amplifier

х

### Yield

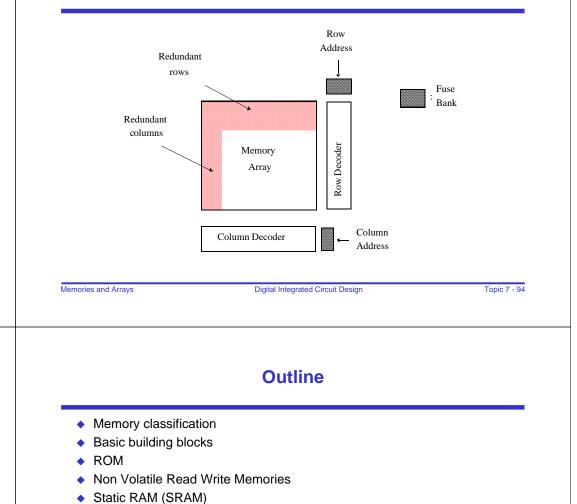

**Redundancy and Error Correction**

Redundancy only

Redundancy

and ECC

100

80

60

40 ·

20 -

0

0

Percent yield

ECC only

### Redundancy

- Dynamic RAM (DRAM)

- Memory peripheral circuit

- Serial access memories

- Content Addressable Memory (CAM)

- Programmable Logic Array

- Reliability and Yield

- Memory trends

500 1000 1500 2000 2500 3000 3500 4000

Average number of failing cells per chip

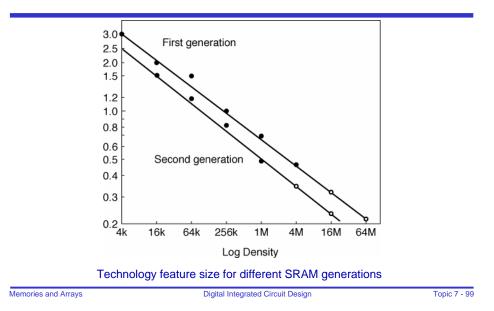

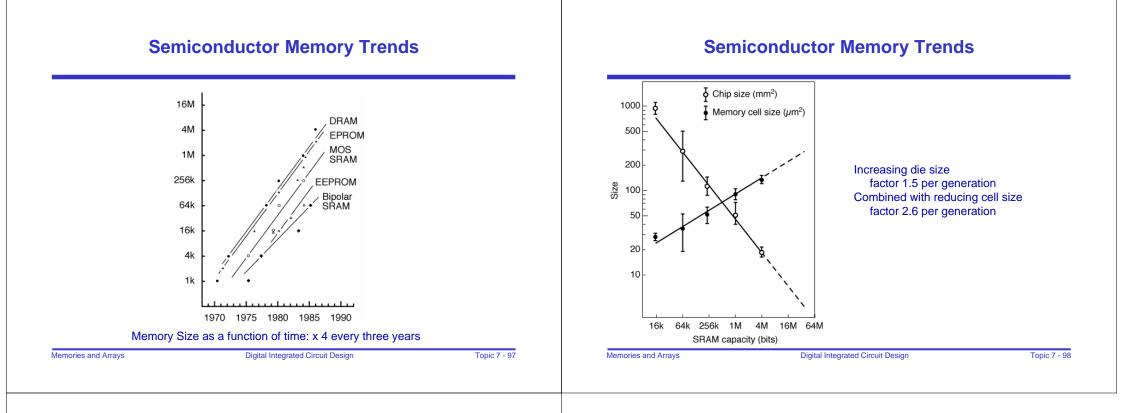

### **Semiconductor Memory Trends**