flickr - AMagill

Architectures of FPGA

Evolvable systems were often built upon commercial reconfigurable Field Programmable Gate Array (FPGA) considering most signals are converted into bit-stream fashion to enhance the design ability by software. Device from the company such as Xilinx and Altera’s are used more often. We learnt from a survey on reconfigurable architecture1 that the architecture can be treated as 3 different parts: system-level architecture, its fabric and function unit.

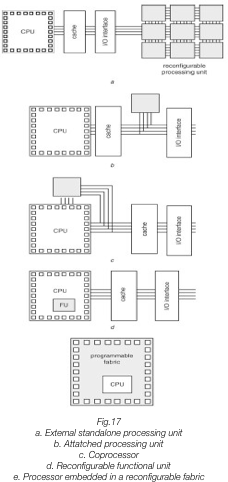

The main architecture is classified into 4 categories (see Fig. 17 ) with different combination of CPU, cache, I/O interface and the reconfigurable processing unit. The difference accounts for the communication cost. A fifth architecture has been introduced because of having an advantage over the other 4 architectures. That is its CPU is implemented on the top of the fabric so that it can either has a hard core with a fix clock frequency or a soft core with a variable clock frequency tuning the resources from the programmable fabric directly rather than communicating via the cache and I/O interface.1

Beneath its system-level architecture, lying the fabric to support it and it is the essential part of the system. The fabric consists of function units and interconnects to link the units, all of them are reconfigurable. The functional units are merely look-up tables(LUT), it is a way to accelerate the rate of interaction with the memory and LUT just takes several input signals to output several signals after a series of gates. The functional units are currently divided into 2 categories, fined grained (FGFU) and coarse grained functional unit (CGFU). FGFU are just a group of LUTs, while CGFU are LUTs with its own memory or even arithmetic logic units (ALU). Therefore, there is a tradeoff of between FGFU and CGFU. FGFU is more flexible, but it consumes more power because many transistors switch at the same time. Moreover more transistors would require larger chip area and longer time delay for switching. Since FGFU is less flexible and need fewer data input because of its memory and integrated ALU, the system is smaller in size and responses faster. If the system can use the CGFU effectively then the flexibility is no more a problem.

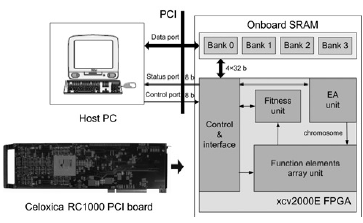

Now we have to consider the interconnections between the functional units because it holds keys of power consumption (about 70% of total power)2 and the delay time of between functions. Note that we need to communicate between them because of the mutation and crossover of the chromosomes need to be taken place. The same classification and trade off exists for the interconnection. On one hand, for the fine-grained interconnection, it switch single transistor at one time hence more flexible but consumes more power. On the other hand, the coarse-grained interconnect switches rows of transistors together hence faster and consumes less power because fewer bits needed to tune the circuit. The detailed diagram of how the genetic algorithm could be applied to the hardware is shown in Fig. 18.3

Fig. 18

This Intrinsic EHW is built on the Celoxica RC 1000 PCI board. It has 3 units for constructing the EWH, namely Fitness unit, EA unit and function element (FE) unit. First the EA will generate 1 chromosome with several copies of mutated ones and store them in the banks, then the Fitness unit evaluate their fitness when each chromosome is divided into genotypes by EA and put into FEs for finding a new offspring. When the best one is found from this generation then it tells the EA to repeat the whole process until the final solution is found. A point to notice is that the crossover operator is not used in this example to speed up the evolution, and the host PC just send the initial setup condition and control signal for this process.

References

1 Todman,T.J., Constantinides, G.A., Wilton, S.J.E., Mencer, O., Luk, W., Cheung., P.Y.K.: Reconfigurable computing: architectures and design methods. IEE PROCEEDINGS. COMPUTERS AND DIGITAL TECHNIQUES 152 (2) pp. 193-207 (2005)

2 Mehta, G., Hunsaker, B., Stander, J., Jones, A.K., Baz, M.: Interconnect customization for a hardware fabric. ACM Transactions on Design Automation of Electronic Systems 11:3 (2009)

3 Wang, J.: Design and implementation of a virtual reconfigurable architecture for different applications of intrinsic evolvable hardware, IET COMPUTERS AND DIGITAL TECHNIQUES 2 (5) pp. 386-400 (2008)