flickr - AMagill

New developments

References

1 Garvie, M., Thompson, A.: Evolution of Self-diagnosing Hardware. Proceedings. NASA/DOD CONFERENCE ON EVOLVABLE HARDWARE. pp. 167-173 (2003)

2 Yang, H., Chen, L., iLu, S., Bu, H., Wang, Y., aLi, J.: A Flexible Bit-Stream Level Evolvable Hardware Platform Based on FPGA. Adaptive Hardware and Systems, 2009. AHS 2009. NASA/ESA Conference on July 29 2009-Aug.1. pp. 51-56 (2009)

3 Torresen, J.: Scalable evolvable hardware applied to road image recognition. Proceedings. The Second NASA/DoD Workshop on Evolvable Hardware. Palo Alto, CA, USA,13-15 July 2000. Publication: Los Alamitos, CA, USA.IEEE Comput. Soc. pp.245-52 (2000)

4 Liu, W.: ATM cell scheduling by function level evolvable hardware. EVOLVABLE SYSTEMS: FROM BIOLOGY TO HARDWARE 1259, pp. 180-192 (1997)

5 Wang, J.: Design and implementation of a virtual reconfigurable architecture for different applications of intrinsic evolvable hardware, IET COMPUTERS AND DIGITAL TECHNIQUES 2 (5) pp. 386-400 (2008)

6 WANG J., PIAO C.H., LEE C.H.: Implementing multi-VRC cores to evolve combinational logic circuits in parallel. Proc. 7th Int. Conf. Evolvable Systems: From Biology To Hardware (ICES), Wuhan, China, September 2007, pp. 23–34 (2007)

7 Chen, S., Li, Y.: A Novel Two-Level Evolutionary Algorithm for Solving Constrained Function Optimization." International Conference on Signal Processing Systems. 15-17 May 2009 pp. 702-706 (2009)

8 Torresen, J.: A divide-and-conquer approach to evolvable hardware. EVOLVABLE SYSTEMS: FROM BIOLOGY TO HARDWARE 1478. pp. 57-65 (1998)

9 Xilinx Virtex-6 data-sheet. Virtex-6 Family Overview. www.xilinx.com/support/documentation/data_sheets/ds150.pdf

In this section, we will have a look on systems that EWH has developed so far, and means that have recently used to improve the qualities of the systems. First, we will look at error detection.

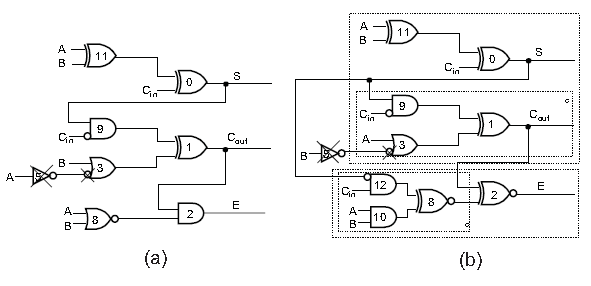

In a circuit, the output produces errors when it suffers from noises or internal circuit failure such as short circuit. Hence some works have been done in these field to improve the accuracy and reliable of the output results. For instance, in M. Garvie and A. Thompson's paper1, they tried to build an evolving Built-in self-test (BIST) circuit upon an adder. Apart from Sum and Carry Out, it has one more output E which is the error signal if anything wrong hence it makes the circuit more reliable.

Fig. 19

In the figure above,1 (a) shows the evolved result for the extrinsic simulation with 14100 generation by using Elitism selection first, and (b) represent the intrinsic case with only 3 more gates with a generation of 15000. Details about why it has 3 more gates can be found in their research paper. Note that the error signal generated is constructed from its own inputs without other testing signals.

Another field of development is the evolving time. Evolving time is critical for very complex systems, less designing period simply means less overhead, hence we need to optimise the time of evolving to its minimum.

First, from the hardware point of view, a suggestion from the Fudan university's research group's paper2, which is namely an adaptive variable-size look-up-table (LUT) array structure, is proposed, it has a variable length JTAG-chain circuit, which is used to improve the resource utilisation rate by directly read and set the bits coming in or out of the system, other than using the developing tool kits and interface provided by manufacturers. Hence it accelerates the speed from bit-stream level instead of gate3 or function level4. Also noteworthy is that their method is used to evolve both combinatorial and sequential circuit since the JFAG can have D flip-flops as the memory elements of a sequential circuit. All circuits they have evolved show a much shorter time compared with the circuits others used to experiment before.

Another suggestion5 is that the system could be evolving in an intrinsic mode on a FPGA. The main advantage of this mode is that the chip offers a pipeline to accelerate the computational speed. Also the interconnections between the fitness evaluation unit, memory and the chromosome generation unit are optimised. Moreover, researchers even tried to embed several cores onto the FPGA board to get the parallel evolving ability.6

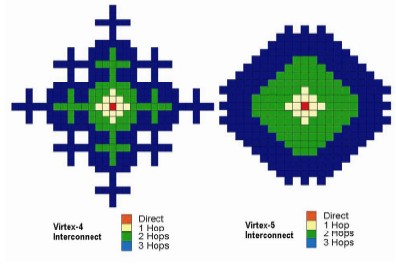

Furthermore, the FPGA manufacture also tried to design better interconnect to increase the information processing speed. Such as the one illustrated in the figure below.

Fig. 20

From the comparison between Virtex-4 and Virtex-5 interconnects, Coupled with the ultra-speed clock technology up to 550 MHz, the company claims that later offers a better connectivity and overall performance.

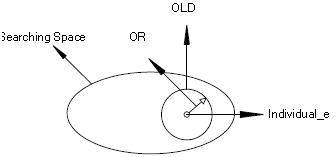

Now we move to see the improvement from the algorithm’s point of view. I Two-Level Evolutionary Algorithm (TLEA) for dealing with Constrained Optimisation was proposed.7 In general, they method involves 2 stages as the second stage is shown in Fig. 21.

Fig. 21

The first stage starts with an OLD searching space which is the same as the way mentioned in our discussions of genetic algorithm from the previous section. The aim of this stage is to quickly find the exact domain where the best solution exists, then the second stage begins with a reinitialisation process which is a bit similar to elitism. It contains several fitter chromosomes named Individual_e and these chromosomes would mutate within the new domain defined by the Optimal Radius (OR) using the Big Mutator, until solution is found. They have proven this two-stages algorithm is better than the original algorithm in terms of speed of convergence, accuracy of finding solutions.

There is another strategy used called the N + 1 mutation strategy.5 It does not need to use the crossover operator because of this the most time consuming process when doing that. Instead, they generate N chromosomes at the first place, and after evaluating their fitness they select the best one then create N + 1 mutated copies of the fitter one. Then they calculate the fitness again and the process continuous. Although they have shown the speed of evolving speed has increased noticeably and the average deviation from the real solution is better than the same one that other group has achieved, the best solution closing to the real solution is occasionally somehow missed.

Other then the two points of view mentioned above, there is also a possible way for tackling the slow involving speed when designing a more complex system which has a scalability problem. A method called Divide and Conquer,8 where the main system is divided into several smaller subsystems which evolve separately and finally integrated, can be used. The result has suggested that this strategy preforms better than evolving the system as a whole.

The development of flexibility of hardware is also crucial. The flexibility of the architecture will determine system's performance such as the evolving time, power consumption, and size of system. As mentioned earlier, the comparison between the fine-grained and coarse-grained types of function unit, same as the one for the interconnect illustrates one reason which gives greater flexibility, because the length of the chromosome or genotype increases. Therefore enabling one to finely tune the circuit more elaborately. On the other hand, it also requires broader data bus to run the system, hence greater power is required to handle the data processing and a lot more memory to store the data. Therefore, the system would be bulky and power hungry. There are several suggestion that may keep the flexibility while deliver a smaller size and lower power system.

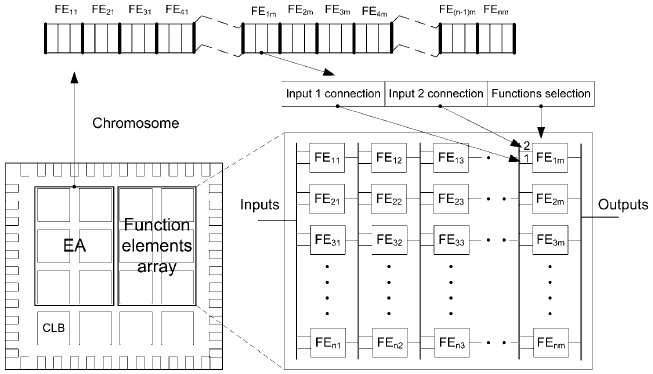

One of the novel proposal is introduced by Wang, J. In his paper5 he suggests a virtual reconfigurable architecture (VRA) on the intrinsic mode EHW implemented on a FPGA. (See Fig. 22 below)

Fig. 22

This architecture contains an algorithm unit, a fitness value calculation unit and a two-dimensional Function Element array unit. The construction is shown in the figure above. The first dimension which consists of a few bits define the function of a FE in a column, and a few more bits of the other dimension define the interactions with the other FE units from the previous column. Together a FE consists of these two dimensions and it represents a single genotype. Then one single column would have several FEs such that the genotypes form a binary encoded chromosome generated by EA unit. The reason that one FE only react with the one from previous column is that in that way the size of the chromosome is restricted in order to evolve fast and gain more computational power. The flexibility being that the first dimension can choose from function level evolution such as the functions of Mean, Greater, Less; or from the gate level evolution such as XOR, OR and AND gates because it just a bunch of LUTs inside the FE.The main differences are the number of bits needed to define the level of operating and the size of the datapath, single wire for gate level and bus line for function level configuration.

Fig. 23

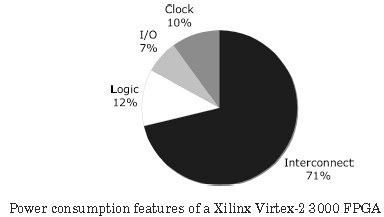

Finally, the power consumption and costs of the board concern us as well. To start with, we will focus on the boards most EHW are implemented on, namely main stream FPGA boards such as the Xilinx Virtex series. Fig. 23 above shows the power distribute on the board.20 As one can notice, most power is operating on the interconnect. One solution towards this problem is to increase the density of transistors by taking advantage of Moore's Law. For a Virtex-6 board9 which doubles the density compared with its predecessor, the manufacturer claims to have 15% lower power consumption while delivering 15% higher performance with 40nm logic process. On the other hand, Fig. 24 shows that changing the feature mix of the board can reduce the cost. The red part illustrates that the more digital signal processing units it uses, the lower the cost of the board would be.

Fig. 24

A good example of intrinsic evolvable hardware -

http://www.informatics.sussex.ac.uk/users/adrianth/ices96/node1.html

NASA’s outer space antenna design using extrinsic evolvable hardware with good pictures -

http://www.genetic-programming.org/gecco2004hc/lohn-paper.pdf