Department of Electrical & Electronic Eng. (EEE) BEng & MEng 2nd Year

ELEC50001 Circuits and Systems (Oct - Dec 2025)

Professor Peter Y. K. Cheung

Department of Electrical & Electronic Eng. (EEE) BEng & MEng 2nd Year |

Aims & Objectives

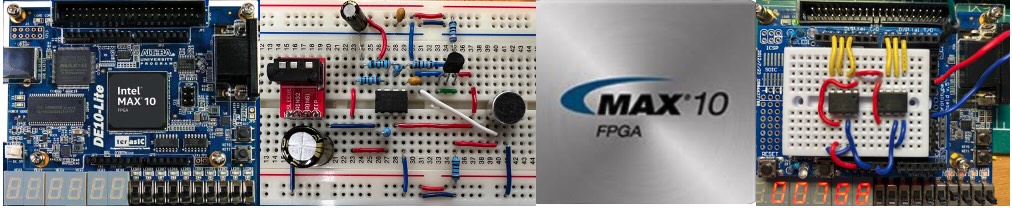

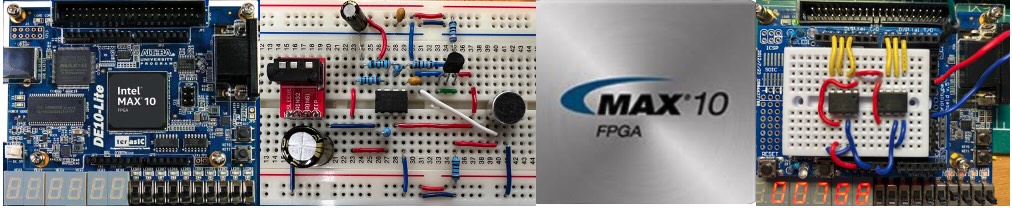

This module builds on the first-year modules relating to analogue and digital circuits, computer architecture, and programming, to teach students how to analyse and design electronic circuits with a system level perspective. The aim of this module is to provide students with the theoretical foundations, the design techniques and hands-on experiences of acquiring physical analogue signals, pre-processing them, converting into digital form, then process these in a digital programmable hardware on a Field Programmable Gate Array (FPGA). Unlike last year's module on circuits, year students will learn to process signals that have noise and electronic hardware that are non-ideal.

By the end of the course, you should be able to:This course is supported by 6 Laboratory Experiments based a Lab-in-a-Box to enable students to conduct all the experiments in-person and at home.

RECOMMENDED TEXTBOOKS

COURSE SCHEDULE AND CONTENTS

Date |

Topics |

Resources |

7 Oct |

||

13 Oct |

||

14 Oct |

||

20 Oct |

||

21 Oct |

||

27 Oct |

||

28 Oct |

||

3-4 Nov |

||

10 Nov |

||

11 Nov |

||

17 Nov |

||

18 Nov |

||

24 Nov |

Audio files: clapping.mp3, hello.mp3, hg2g.mp3 , hg2g(short).mp3 |

|

25 Nov |

||

2 Dec |

Bonus Lecture

|

|

9 -10 Dec |

LECTURE NOTES

Lecture 1 - Introduction to circuits & systems (notes) Lecture 2 - Amplification and Single-Rail Op-amp (notes) Lecture 3 - Understanding Op-amp Specification (notes) Lecture 4 - Understanding Op-amp Models (notes) Lecture 5 - Op-amp Applications (notes) Lecture 6 - Active Filters (notes) Lecture 7 - Digital Design with FPGAs (notes) Lecture 8 - SystemVerilog HDL (notes) Lecture 9 - Counters and Shift Registers (notes) Lecture 10 - DAC Conversion (notes) Lecture 11 - Finite State Machines (notes) Lecture 12 - Analogue-to-Digital Conversion (notes) Lecture 13 - Lab 6 & Challenges Explained (notes) Lecture 14 - Timing Constraints (notes) Lecture 15 - memories (notes) Lecture 16 - spi2dac explained (notes)

LAB INSTRUCTIONS

Lab 1- Amplification & Single-rail Op-Amp Lab 2 - Op-amp Applications Lab 3 - Introduction to Quartus & DE10-Lite Lab 4 - Sequential Circuits Lab 5 - DAC and Function Generator Lab 6 - ADC & Echo Synthesizer Challenges

PROBLEM SHEETS

Problem Sheet 1 (solutions) Problem Sheet 2 (solutions) Problem Sheet 3 (solutions) Problem Sheet 4 (solutions) Problem Sheet 5 (solutions) Problem Sheet 6 (solutions) Problem Sheet 7 (solutions)

Past Examination Papers

Exam Paper 2022 (solutions) Exam Paper 2023 (solutions) Exam Paper 2024 (solutions) Exam Paper 2025 (solutions)