Department of Electrical &

Electronic Engineering

Electrical & Electronic Eng.

(EEE) BEng & MEng 2nd Year

Electronic and Information Eng. (EIE) BEng &

MEng 2nd Year

E2.1 Digital Electronics

2 (Oct - Dec 2019)

Professor Peter Y. K. Cheung |

|

Aims & Objectives

The aims of the course are:

- To learn about digital circuits work

- To learn how to implement reasonably complicated circuits on FPGAs

- To learn how to design with Verilog HDL

By the end of the course, you should be able to:

- analyse the operation of synchronous digital systems

- synthesize a synchronous digital system to meet a specification

- determine the worst-case propagation delay of a combinational circuit

- evaluate the performance of A/D and D/A conversion circuits

- design arithmetic circuits to meet a specification and determine the propagation delay

- design of finite state machines

- design using Verilog HDL

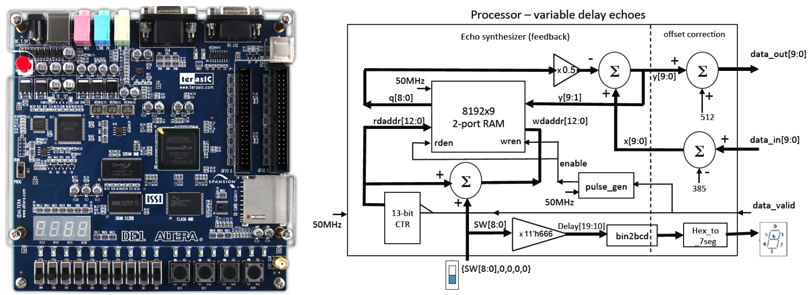

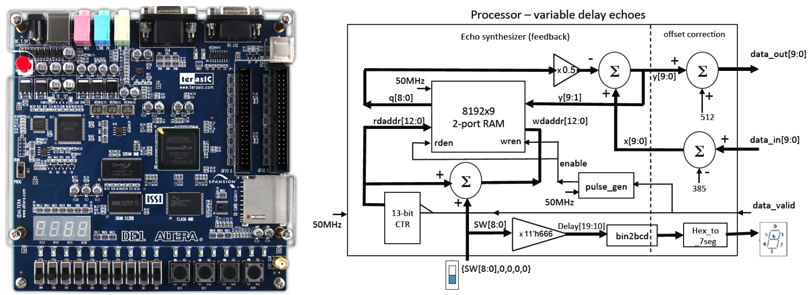

This course is supported a 4-week Laboratory Experiment - Experiment VERI starting in the middle of the Autumn term. You will be working in pairs, using the Terasic/Altera's DE1-SoC board with a daughter board extension.

Each pair of students can also sign out one board (every two students) from the EEE Stores. Please return the board by the end of the Spring term in 2018.

Lecture Notes

Lecture 1 Introduction to digital logic (8 Oct - Panopto recording) (notes 2-per page)

Lecture 2 Introduction to FPGAs (8 Oct - Panopto recording) (notes 2-per page)

Lecture 3 Verilog HDL - Part 1 (14 Oct - Panopto recording) (notes 2-per page)

Lecture 4 Verilog HDL - Part 2 (15 Oct - Panopto recording) (notes 2-per page)

Lecture 5 Counters and shift registers (21,22 Oct - Panopto recording part 1, 2) (notes 2-per page)

Lecture 6 Finite State Machines - Part 1 (22 Oct - Panopto recording) (notes 2-per page)

Lecture 7 Finite State Machines - Part 2 (28 Oct - Panopto recording) (notes 2-per page)

Lecture 8 Timing constraints (29 Oct - Panopto recording part 1 part 2) (notes 2-per page)

Lecture 9 D-to-A converters (ADI Handbook Chap 3) (4 Nov - Panopto recording) (notes 2-per page)

Lecture 10 Experiment VERI - an overview (5 Nov - Panopto recording) (notes 2-per page)

Lecture 11 A-to-D converters (ADC architectures - A tutorial) (18 Nov - Panopto recording) (notes 2-per page)

Lecture 12 Serial Peripheral Interface (SPI) (19 Nov - Panopto recording part_1 part_2) (R12.1 DAC datasheet) (notes 2-per page)

Lecture 13 Memory circuits (25 Nov - Panopto recording_1 2) (notes 2-per page)

Lecture 14 Part 4 of VERI experiment (26 Nov - Panopto recording) (notes 2-per page)

Revision Lecture 1 (28 April - MS Teams recording)

Revision Lecture 2 (5 May - MS Teams recording)

Tutorial Problem Sheets

Tutorial Problems |

Useful Resources |

|

R1.1 FPGA and CPLD Architectures: A Tutorial

R1.2 Cyclone V Device Handbook (vol 1)

R1.3 Introduction to Quartus II Software

R1.4 DE1 User's Manual

|

|

|

|

|

|

|

|

|

|

|

Problem Classes

Problem Class 1

Problem Class 2

The Laboratory Experiment (Experiment Webpage HERE)

This course is supported by a 4-week experiment in the Laboratory.

Details of this experiment can be found HERE.

Past Examination Papers

June 2017 (Paper,Solutions)

June 2018 (Paper,Solutions)

June 2019 (Paper, Solutions)

Student Online Lecturer Evaulation (SOLE)

Student's evaluation and comments for this module from 2018_19 session (PDF)

Other DE1 & Cyclone V Resources

Quartus Prime Software free web-edition (Download page)

Quartus & DE1-SoC Tutorial Page (containing MANY tutorials, probably too many. Be selective!)

Cyclone V Device Handbooks

Vol 1: Device Interface & Integration

Vol 2: Transceivers

Vol 3: Hard Processor System

Useful links

Verilog HDL Quick Reference Card

A very good tutorial on IEEE Logic

Symbols

An excellent tutorial on Verilog HDL

Altera's free tutorial on Verilog HDL (interactive video class lasting 45 minutes)

On-line Verilog HDL Quick Reference Guide (free)

This page is maintained by Peter Cheung

Last updated: 29 April 2020